## **FEATURES**

- ▶ 16-bit monotonicity over temperature

- ▶ Microprocessor compatible with read-back capability

- ▶ Unipolar or bipolar output

- Multiplying capability

- ▶ Low power dissipation: 100 mW typical

#### **APPLICATIONS**

- Instrumentation

- Automatic test equipment

- Industrial automation

- Energy grid systems

- Aerospace

#### **GENERAL DESCRIPTION**

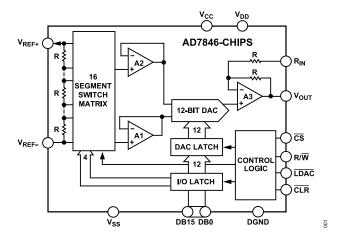

The AD7846-CHIPS is a 16-bit digital-to-analog converter (DAC) constructed with the Analog Devices, Inc., LC $^2$ MOS process. The device has V<sub>REF+</sub> and V<sub>REF-</sub> reference inputs and an on-chip output amplifier that can be configured to give a unipolar output range (0 V to +5 V or 0 V to +10 V) or bipolar output ranges (±5 V or ±10 V).

The DAC uses a segmented architecture. The four MSBs in the DAC latch select one of the segments in a 16-resistor string. Both taps of the segment are buffered by amplifiers and fed to a 12-bit DAC, which provides a further 12 bits of resolution. This architecture ensures 16-bit monotonicity. Excellent integral linearity results from tight matching between the input offset voltages of the two buffer amplifiers.

# LC2MOS 16-Bit Voltage Output DAC

In addition to the excellent accuracy specifications, the AD7846-CHIPS also offers a comprehensive microprocessor interface. There are 16 data input and output pins, plus control lines ( $\overline{\text{CS}}$ , R/ $\overline{\text{W}}$ ,  $\overline{\text{LDAC}}$ , and  $\overline{\text{CLR}}$ ). R/ $\overline{\text{W}}$  and  $\overline{\text{CS}}$  allow writing to and reading from the input and output latch, and this read-back function is useful in ATE applications.  $\overline{\text{LDAC}}$  allows simultaneous updating of DACs in a multiDAC system, and the  $\overline{\text{CLR}}$  line resets the contents of the DAC latch to 00 ... 000 or 10 ... 000 depending on the state of R/ $\overline{\text{W}}$ , which means that the DAC output can be reset to 0 V in both unipolar and bipolar configurations.

Additional application and technical information can be found in the AD7846 data sheet.

#### **PRODUCT HIGHLIGHTS**

- 16-Bit Monotonicity. The guaranteed 16-bit monotonicity over temperature makes the AD7846-CHIPS ideal for closed-loop applications.

- Readback. The ability to read back the DAC register contents minimizes software routines when the AD7846-CHIPS is used in automatic test equipment systems.

- **3.** Power Dissipation. A power dissipation of 100 mW makes the AD7846-CHIPS a low power, high accuracy DAC.

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

#### **TABLE OF CONTENTS**

| Features 1                      | Absolute Max  |

|---------------------------------|---------------|

| Applications1                   | ESD Cautio    |

| General Description1            | Pin Configura |

| Product Highlights1             | Outline Dimer |

| Functional Block Diagram1       |               |

| Specifications3                 | Recomme       |

| AC Performance Characteristics5 | Ordering Gu   |

| Timing Characteristics5         | _             |

#

## **REVISION HISTORY**

11/2023—Revision 0: Initial Version

analog.com Rev. 0 | 2 of 11

# **SPECIFICATIONS**

$V_{DD} = +14.25 \text{ V to } +15.75 \text{ V}, V_{SS} = -14.25 \text{ V to } -15.75 \text{ V}, \text{ and } V_{CC} = +4.75 \text{ V to } +5.25 \text{ V}. V_{OUT} \text{ loaded with 2 k}\Omega, 1000 \text{ pF to 0 V}, V_{REF+} = +5 \text{ V}, \text{ and R}_{IN} \text{ connected to 0 V}. \text{ All specifications T}_{MIN} \text{ to T}_{MAX}, \text{ unless otherwise noted}.$

Table 1. Specifications

| Parameter <sup>1</sup>                                                        | Min                 | Тур | Max                 | Unit       | Test Conditions/Comments                                     |

|-------------------------------------------------------------------------------|---------------------|-----|---------------------|------------|--------------------------------------------------------------|

| RESOLUTION                                                                    |                     | 16  |                     | Bits       |                                                              |

| UNIPOLAR OUTPUT                                                               |                     |     |                     |            | V <sub>REF</sub> -= 0 V, V <sub>OUT</sub> = 0 V to +10 V     |

| Relative Accuracy at 25°C                                                     |                     | ±12 |                     | LSB        | 1 LSB = 153 μV                                               |

| T <sub>MIN</sub> to T <sub>MAX</sub>                                          |                     |     | ±16                 | LSB        |                                                              |

| Differential Nonlinearity Error                                               |                     |     | ±1                  | LSB        | All grades guaranteed monotonic                              |

| Gain Error at 25°C                                                            |                     | ±12 |                     | LSB        | $V_{OUT}$ load = 10 M $\Omega$                               |

| T <sub>MIN</sub> to T <sub>MAX</sub>                                          |                     |     | ±16                 | LSB        |                                                              |

| Offset Error at 25°C                                                          |                     | ±12 |                     | LSB        |                                                              |

| T <sub>MIN</sub> to T <sub>MAX</sub>                                          |                     |     | ±16                 | LSB        |                                                              |

| Gain Temperature Coefficient <sup>2</sup>                                     |                     | ±1  |                     | ppm FSR/°C |                                                              |

| Offset Temperature Coefficient <sup>2</sup>                                   |                     | ±1  |                     | ppm FSR/°C |                                                              |

| BIPOLAR OUTPUT                                                                |                     |     |                     |            | V <sub>REF</sub> - = -5 V, V <sub>OUT</sub> = -10 V to +10 V |

| Relative Accuracy at 25°C                                                     |                     | ±6  |                     | LSB        | 1 LSB = 305 µV                                               |

| T <sub>MIN</sub> to T <sub>MAX</sub>                                          |                     |     | ±8                  | LSB        | · ·                                                          |

| Differential Nonlinearity Error                                               |                     |     | ±1                  | LSB        | All grades guaranteed monotonic                              |

| Gain Error at 25°C                                                            |                     | ±6  |                     | LSB        | $V_{OUT}$ load = 10 M $\Omega$                               |

| T <sub>MIN</sub> to T <sub>MAX</sub>                                          |                     |     | ±16                 | LSB        | 001                                                          |

| Offset Error at 25°C                                                          |                     | ±6  |                     | LSB        | $V_{OUT}$ load = 10 M $\Omega$                               |

| T <sub>MIN</sub> to T <sub>MAX</sub>                                          |                     |     | ±16                 | LSB        | 001                                                          |

| Bipolar Zero Error at 25°C                                                    |                     | ±6  |                     | LSB        |                                                              |

| T <sub>MIN</sub> to T <sub>MAX</sub>                                          |                     |     | ±12                 | LSB        |                                                              |

| Gain Temperature Coefficient <sup>2</sup>                                     |                     | ±1  |                     | ppm FSR/°C |                                                              |

| Offset Temperature Coefficient <sup>2</sup>                                   |                     | ±1  |                     | ppm FSR/°C |                                                              |

| Bipolar Zero Temperature Coefficient <sup>2</sup>                             |                     | ±1  |                     | ppm FSR/°C |                                                              |

| REFERENCE INPUT                                                               |                     |     |                     | 111        |                                                              |

| Input Resistance                                                              | 20                  |     |                     | kΩ         | Resistance from V <sub>REF+</sub> to V <sub>REF-</sub>       |

|                                                                               |                     |     | 40                  | kΩ         | Typically 30 kΩ                                              |

| V <sub>REF+</sub> Range                                                       | V <sub>SS</sub> + 6 |     | V <sub>DD</sub> - 6 | V          | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                      |

| V <sub>REF</sub> _ Range                                                      | V <sub>SS</sub> + 6 |     | V <sub>DD</sub> - 6 | V          |                                                              |

| OUTPUT CHARACTERISTICS                                                        | 133 1               |     | - 00 -              |            |                                                              |

| Output Voltage Swing                                                          | V <sub>SS</sub> + 4 |     | V <sub>DD</sub> - 3 | V          |                                                              |

| Resistive Load                                                                | 2                   |     | VDU O               | kΩ         | To 0 V                                                       |

| Capacitive Load                                                               | -                   |     | 1000                | pF         | To 0 V                                                       |

| Output Resistance                                                             |                     | 0.3 | 1000                | Ω          | 1001                                                         |

| Short Circuit Current                                                         |                     | ±25 |                     | mA         | To 0 V or any power supply                                   |

| DIGITAL INPUTS                                                                |                     |     |                     | 110.4      | 10 0 1 of any points supply                                  |

| Input High Voltage (V <sub>IH</sub> )                                         | 2.4                 |     |                     | V          |                                                              |

| Input Low Voltage (V <sub>IL</sub> )                                          | 2.4                 |     | 0.8                 | V          |                                                              |

| Input Current (I <sub>IN</sub> )                                              |                     |     | ±10                 | μA         |                                                              |

| Input Capacitance (C <sub>IN</sub> ) <sup>2</sup>                             |                     |     | 10                  | pF         |                                                              |

| DIGITAL OUTPUTS                                                               |                     |     | 10                  | Pi         |                                                              |

| Output Low Voltage (V <sub>OL</sub> )                                         |                     |     | 0.4                 | V          | Sink current (I <sub>SINK</sub> ) = 1.6 mA                   |

| Output Low Voltage (V <sub>OL</sub> )  Output High Voltage (V <sub>OH</sub> ) | 4.0                 |     | U. <del>4</del>     | V          | Source current ( $I_{SOURCE}$ ) = 400 $\mu$ A                |

| Floating State Leakage Current                                                | 7.0                 |     | ±10                 |            | DB0 to DB15 = 0 V to V <sub>CC</sub>                         |

| i idaling diale Leakage Guilell                                               |                     |     | ±10                 | μA         | א מו א מ – פו מת מו ממת                                      |

analog.com Rev. 0 | 3 of 11

## **SPECIFICATIONS**

Table 1. Specifications (Continued)

| Parameter <sup>1</sup>                     | Min   | Тур | Max    | Unit  | Test Conditions/Comments  |

|--------------------------------------------|-------|-----|--------|-------|---------------------------|

| POWER REQUIREMENTS <sup>3</sup>            |       |     |        |       |                           |

| $V_{DD}$                                   | +11.4 |     | +15.75 | V     |                           |

| $V_{SS}$                                   | -11.4 |     | -15.75 | V     |                           |

| V <sub>CC</sub>                            | +4.75 |     | +5.25  | V     |                           |

| V <sub>DD</sub> Current (I <sub>DD</sub> ) |       |     | 5      | mA    | V <sub>OUT</sub> unloaded |

| V <sub>SS</sub> Current (I <sub>SS</sub> ) |       |     | 5      | mA    | V <sub>OUT</sub> unloaded |

| V <sub>CC</sub> Current (I <sub>CC</sub> ) |       |     | 1      | mA    |                           |

| Power Supply Sensitivity <sup>4</sup>      |       |     | 1.5    | LSB/V |                           |

| Power Dissipation                          |       | 100 |        | mW    | V <sub>OUT</sub> unloaded |

<sup>&</sup>lt;sup>1</sup> Temperature range is-40°C to +105°C.

analog.com Rev. 0 | 4 of 11

<sup>&</sup>lt;sup>2</sup> Guaranteed by design and characterization, not production tested.

$<sup>^3</sup>$  The AD7846-CHIPS is functional with power supplies of  $\pm 12$  V. See the Typical Performance Characteristics section in the AD7846 data sheet.

$<sup>^4</sup>$   $\,$  Sensitivity of gain error, offset error, and bipolar zero error to  $\rm V_{DD}$  and  $\rm V_{SS}$  variations.

## **SPECIFICATIONS**

#### **AC PERFORMANCE CHARACTERISTICS**

These characteristics are included for design guidance and are not subject to test.  $V_{REF+}$  = +5 V,  $V_{DD}$  = +14.25 V to +15.75 V,  $V_{SS}$  = -14.25 V to -15.75 V,  $V_{CC}$  = +4.75 V to +5.25 V, and  $R_{IN}$  connected to 0 V, unless otherwise noted. The minimum, typical, and maximum values are the limits at  $T_{MIN}$  to  $T_{MAX}$ .

Table 2. AC Performance Characteristics

| Parameter                                      | Min | Тур | Max | Unit   | Test Conditions/Comments                                                           |

|------------------------------------------------|-----|-----|-----|--------|------------------------------------------------------------------------------------|

| Output Settling Time <sup>1</sup>              |     |     | 6   | μs     | To 0.006% FSR, V <sub>OUT</sub> loaded, V <sub>REF</sub> = 0 V, typically 3.5 μs   |

|                                                |     |     | 9   | μs     | To 0.003% FSR, $V_{OUT}$ loaded, $V_{REF-} = -5 \text{ V}$ , typically 6.5 $\mu s$ |

| Slew Rate                                      |     | 7   |     | V/µs   |                                                                                    |

| Digital-to-Analog Glitch                       |     |     |     |        |                                                                                    |

| Impulse                                        |     | 70  |     | nV-sec | DAC alternately loaded with 10 0000 and 01 1111, V <sub>OUT</sub> unloaded         |

| AC Feedthrough                                 |     | 0.5 |     | mV p-p | $V_{REF-}$ = 0 V, $V_{REF+}$ = 1 V RMS, 10 kHz sine wave, DAC loaded with all 0s   |

| Digital Feedthrough                            |     | 10  |     | nV-sec | DAC alternately loaded with all 1s and all 0s, $\overline{\text{CS}}$ high         |

| Output Noise Voltage Density, 1 kHz to 100 kHz |     | 50  |     | nV/√Hz | Measured at $V_{OUT}$ , DAC loaded with 0111011 11, $V_{REF+}$ = $V_{REF-}$ = 0 V  |

<sup>1</sup> LDAC = 0. Settling time does not include deglitching time of 2.5 μs (typ).

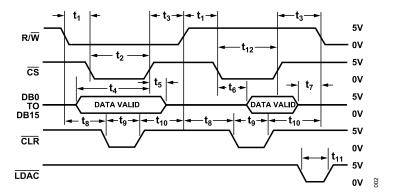

#### **TIMING CHARACTERISTICS**

$V_{DD}$  = +14.25 V to +15.75 V,  $V_{SS}$  = -14.25 V to -15.75 V, and  $V_{CC}$  = +4.75 V to +5.25 V, unless otherwise noted. The minimum, typical, and maximum value limits are  $T_{MIN}$  to  $T_{MAX}$ .

Table 3. Timing Specifications

| Parameter <sup>1</sup>      | Min | Тур | Max | Unit | Test Conditions/Comments                      |

|-----------------------------|-----|-----|-----|------|-----------------------------------------------|

| t <sub>1</sub>              | 0   |     |     | ns   | R/W to CS setup time                          |

| $t_2$                       | 60  |     |     | ns   | CS pulse width (write cycle)                  |

| $t_3$                       | 0   |     |     | ns   | $R/\overline{W}$ to $\overline{CS}$ hold time |

| $t_4$                       | 60  |     |     | ns   | Data setup time                               |

| $t_5$                       | 0   |     |     | ns   | Data hold time                                |

| $t_6^2$                     |     |     | 120 | ns   | Data access time                              |

| t <sub>7</sub> <sup>3</sup> | 10  |     |     | ns   | Bus relinquish time                           |

|                             |     |     | 60  | ns   |                                               |

| $t_8$                       | 0   |     |     | ns   | CLR setup time                                |

| t <sub>9</sub>              | 70  |     |     | ns   | CLR pulse width                               |

| t <sub>10</sub>             | 0   |     |     | ns   | CLR hold time                                 |

| t <sub>11</sub>             | 70  |     |     | ns   | LDAC pulse width                              |

| t <sub>12</sub>             | 130 |     |     | ns   | CS pulse width (read cycle)                   |

Timing specifications are sample tested at 25°C to ensure compliance. All input control signals are specified with rise time  $(t_R)$  = fall time  $(t_F)$  = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

analog.com Rev. 0 | 5 of 11

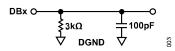

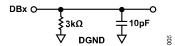

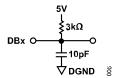

<sup>&</sup>lt;sup>2</sup> t<sub>6</sub> is measured with the load circuits of Figure 3 and Figure 4 and defined as the time required for an output to cross 0.8 V or 2.4 V.

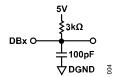

<sup>&</sup>lt;sup>3</sup> t<sub>7</sub> is defined as the time required for an output to change 0.5 V when loaded with the circuits of Figure 5 and Figure 6.

## **SPECIFICATIONS**

# **Timing Diagrams**

Figure 2. Timing Diagram

Figure 3. Load Circuit for Access Time (t<sub>6</sub>)—High Z to V<sub>OH</sub>

Figure 4. Load Circuits for Bus Relinquish Time ( $t_6$ )—High Z to  $V_{OL}$

Figure 5. Load Circuit for Access Time (t<sub>7</sub>)—High Z to V<sub>OH</sub>

Figure 6. Load Circuits for Bus Relinquish Time ( $t_7$ )—High Z to  $V_{OL}$

analog.com Rev. 0 | 6 of 11

Data Sheet

# AD7846-CHIPS

# **ABSOLUTE MAXIMUM RATINGS**

Table 4. Absolute Maximum Ratings

| Parameter                             | Rating                                                            |

|---------------------------------------|-------------------------------------------------------------------|

| V <sub>DD</sub> to DGND               | −0.4 V to +17 V                                                   |

| V <sub>CC</sub> to DGND               | -0.4 V, V <sub>DD</sub> + 0.4 V, or +7 V (whichever is            |

|                                       | lower)                                                            |

| V <sub>SS</sub> to DGND               | +0.4 V to -17 V                                                   |

| V <sub>REF+</sub> to DGND             | V <sub>DD</sub> + 0.4 V, V <sub>SS</sub> - 0.4 V                  |

| V <sub>REF</sub> - to DGND            | V <sub>DD</sub> + 0.4 V, V <sub>SS</sub> - 0.4 V                  |

| V <sub>OUT</sub> to DGND <sup>1</sup> | $V_{DD}$ + 0.4 V, $V_{SS}$ – 0.4 V, or ±10 V (whichever is lower) |

| R <sub>IN</sub> to DGND               | V <sub>DD</sub> + 0.4 V, V <sub>SS</sub> - 0.4 V                  |

| Digital Input Voltage to DGND         | -0.4 V to V <sub>CC</sub> + 0.4 V                                 |

| Digital Output Voltage to DGND        | -0.4 V to V <sub>CC</sub> + 0.4 V                                 |

| Power Dissipation                     |                                                                   |

| To 75°C                               | 1000 mW                                                           |

| Derates Above 75°C                    | 10 mW/°C                                                          |

| Temperature                           |                                                                   |

| Operating Range                       | -40°C to +105°C                                                   |

| Storage Range                         | -65°C to +150°C                                                   |

V<sub>OUT</sub> can be shorted to DGND, V<sub>DD</sub>, V<sub>SS</sub>, or V<sub>CC</sub> provided that the power dissipation of the die is not exceeded.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. 0 | 7 of 11

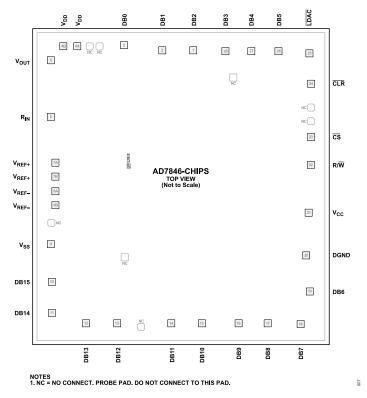

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 7. Pad Configuration

Table 5. Pad Function Descriptions

| Pad No. | Mnemonic           | Pad Type | X-Axis | Y-Axis | Description                                                                                                         |

|---------|--------------------|----------|--------|--------|---------------------------------------------------------------------------------------------------------------------|

| 1       | DB2                | Single   | +158   | +1759  | Data Input and Output.                                                                                              |

| 2       | DB1                | Single   | -240   | +1759  | Data Input and Output.                                                                                              |

| 3       | DB0                | Single   | -735   | +1825  | Data Input and Output, LSB.                                                                                         |

| 4A      | V                  | Double   | -1335  | +1812  | Positive Supply for the Analog Circuitry, 15 V Nominal.                                                             |

| 4B      | V <sub>DD</sub>    | Double   | -1515  | +1812  | Fositive Supply for the Analog Circuity, 15 v Norminal.                                                             |

| 5       | V <sub>OUT</sub>   | Single   | -1675  | +1631  | DAC Output.                                                                                                         |

| 6       | R <sub>IN</sub>    | Single   | -1675  | +901   | Input to Summing Resistor of the DAC Output Amplifier. R <sub>IN</sub> is used to select the output voltage ranges. |

| 7A      | \\                 | Daubla   | -1617  | +312   | VPFF I leave The DAC is excepted for VPFF I = 5 V                                                                   |

| 7B      | V <sub>REF+</sub>  | Double   | -1617  | +132   | VREF+ Input. The DAC is specified for VREF+ = 5 V.                                                                  |

| 8A      | W                  | Daubla   | -1617  | -56    | VPFF Input For unincler energian connect VPFF to 0.V and for hinder energian connect it to 5.V                      |

| 8B      | V <sub>REF</sub> - | Double   | -1617  | -236   | VREF- Input. For unipolar operation, connect VREF- to 0 V, and for bipolar operation, connect it to -5 V.           |

| 9       | V <sub>SS</sub>    | Single   | -1676  | -738   | Negative Supply for the Analog Circuitry, −15 V Nominal.                                                            |

| 10      | DB15               | Single   | -1662  | -1223  | Data Input and Output, MSB.                                                                                         |

| 11      | DB14               | Single   | -1662  | -1624  | Data Input and Output.                                                                                              |

| 12      | DB13               | Single   | -1223  | -1756  | Data Input and Output.                                                                                              |

| 13      | DB12               | Single   | -821   | -1756  | Data Input and Output.                                                                                              |

| 14      | DB11               | Single   | -124   | -1756  | Data Input and Output.                                                                                              |

| 15      | DB10               | Single   | +270   | -1756  | Data Input and Output.                                                                                              |

| 16      | DB9                | Single   | +744   | -1758  | Data Input and Output.                                                                                              |

| 17      | DB8                | Single   | +1118  | -1758  | Data Input and Output.                                                                                              |

| 18      | DB7                | Single   | +1541  | -1767  | Data Input and Output.                                                                                              |

| 19      | DB6                | Single   | +1660  | -1347  | Data Input and Output.                                                                                              |

| 20      | DGND               | Single   | +1613  | -883   | Ground for the Digital Circuitry.                                                                                   |

| 21      | V <sub>CC</sub>    | Single   | +1645  | -333   | Positive Supply for the Digital Circuitry, 5 V Nominal.                                                             |

analog.com Rev. 0 | 8 of 11

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 5. Pad Function Descriptions (Continued)

| Pad No. | Mnemonic | Pad Type | X-Axis  | Y-Axis  | Description                                                                                     |

|---------|----------|----------|---------|---------|-------------------------------------------------------------------------------------------------|

| 22      | R/W      | Single   | +1674   | +283    | R/W Input. This pin can be used to load data to the DAC or to read back the DAC latch contents. |

| 23      | CS       | Single   | +1676   | +643    | Chip Select Input. This pin selects the device.                                                 |

| 24      | CLR      | Single   | +1676   | +1329   | Clear Input. The DAC can be cleared to 000000 or 100000.                                        |

| 25      | LDAC     | Single   | +1654   | 1720    | Asynchronous Load Input to the DAC.                                                             |

| 26      | DB5      | Single   | +1256   | +1747   | Data Input and Output.                                                                          |

| 27      | DB4      | Single   | +907    | +1747   | Data Input and Output.                                                                          |

| 28      | DB3      | Single   | +573    | +1747   | Data Input and Output.                                                                          |

| N/A     | NC       | Single   | +675    | +1409   | Probe pad. Do not connect to this pad.                                                          |

| N/A     | NC       | Single   | -725    | -908    | Probe pad. Do not connect to this pad.                                                          |

| N/A     | NC       | Single   | -1048.5 | +1809.4 | Probe pad. Do not connect to this pad.                                                          |

| N/A     | NC       | Single   | -1174.5 | +1809.4 | Probe pad. Do not connect to this pad.                                                          |

| N/A     | NC       | Single   | -1669   | -464.9  | Probe pad. Do not connect to this pad.                                                          |

| N/A     | NC       | Single   | -515    | -1803.9 | Probe pad. Do not connect to this pad.                                                          |

| N/A     | NC       | Single   | +1675   | +846.5  | Probe pad. Do not connect to this pad.                                                          |

| N/A     | NC       | Single   | +1675.4 | +1021   | Probe pad. Do not connect to this pad.                                                          |

# Table 6. Output Voltage Ranges

| Output Range (V) | V <sub>REF+</sub> (V) | V <sub>REF-</sub> (V) | R <sub>IN</sub> (V) |

|------------------|-----------------------|-----------------------|---------------------|

| 0 to +5          | +5                    | 0                     | V <sub>OUT</sub>    |

| 0 to +10         | +5                    | 0                     | 0                   |

| +5 to −5         | +5                    | -5 V                  | V <sub>OUT</sub>    |

| +5 to −5         | +5                    | 0                     | +5                  |

| +10 to -10       | +5                    | <b>-</b> 5            | 0                   |

analog.com Rev. 0 | 9 of 11

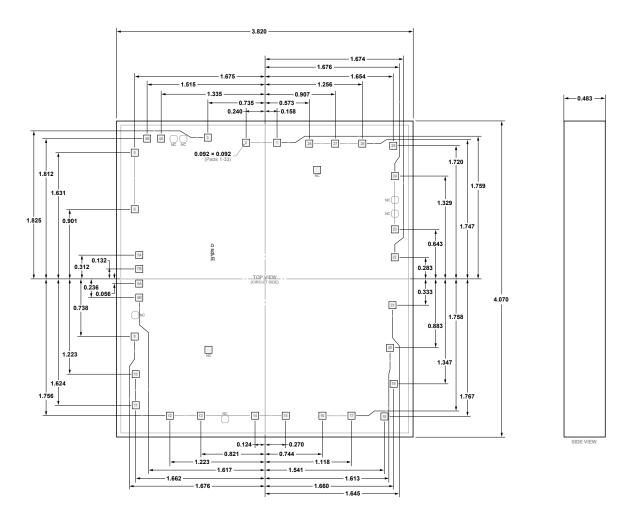

## **OUTLINE DIMENSIONS**

Figure 8. 28-Pad Bare Die [CHIP] (C-28-3) Dimensions shown in millimeters

## DIE SPECIFICATIONS AND ASSEMBLY RECOMMENDATIONS

Table 7. Die Specifications

| Parameter              | Value                                           | Unit |

|------------------------|-------------------------------------------------|------|

| Die Size               | 3820 × 4070                                     | μm   |

| Thickness              | 483                                             | μm   |

| Bond Pad               | 92 × 92                                         | μm   |

| Minimum Bond Pad Pitch | 180                                             | μm   |

| Bond Pad Composition   | 1.0 Aluminum (Al)/Silicon (Si), 0.5 Copper (Cu) | %    |

Table 8. Assembly Recommendations

| Assembly Component | Recommendation                |

|--------------------|-------------------------------|

| Die Attach         | Epoxy dispense                |

| Bonding Method     | Thermosonic gold ball bonding |

| Bonding Sequence   | Bond Pad 20 (DGND) first      |

analog.com Rev. 0 | 10 of 11

## **OUTLINE DIMENSIONS**

# **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description    | Package Option |

|--------------------|-------------------|------------------------|----------------|

| AD7846-CHIPS       | -40°C to +105°C   | 28-Pad Bare Die [CHIP] | C-28-3         |

<sup>&</sup>lt;sup>1</sup> The AD7846-CHIPSAD7846-CHIPS is a RoHS compliant part.