# 6-Channel, 14-Bit, Current Output DAC with On-Chip Reference, SPI Interface

### **FEATURES**

- ▶ 6-channel, current output DAC

- ▶ 14-bit resolution

- ▶ Programmable output current ranges

- Channel 0: 0 mA to 300 mA, -60 mA to +300 mA, -60 mA to 0 mA

- ▶ Channel 1: 0 mA to 140 mA, 0 mA to 250 mA

- ▶ Channel 2: 0 mA to 55 mA, 0 mA to 150 mA

- Channel 3, Channel 4, Channel 5: 0 mA to 45 mA, 0 mA to 100 mA

- ▶ All current sourcing output ranges scale back by up to 0.5×

- ▶ 1.25 V, on-chip voltage reference

- ▶ Integrated precision reference resistor

- ▶ SPI interface

- Reset function

- Output current monitor

- ▶ Compliance voltage monitor

- ▶ Die temperature monitor

- Integrated thermal shutdown

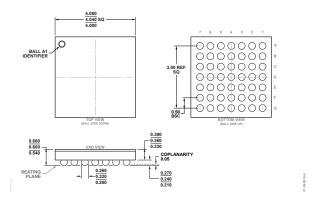

- ▶ 49-ball, 4 mm × 4 mm WLCSP package

- ▶ Operating temperature: -40°C to +105°C

### **APPLICATIONS**

- Photonics control

- ▶ LED driver programmable current source

- Current mode biasing

### **GENERAL DESCRIPTION**

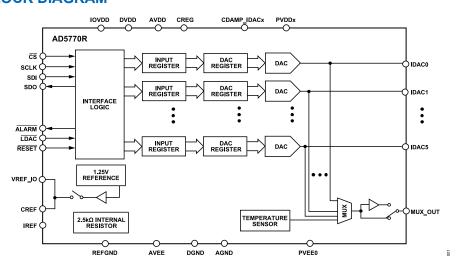

The AD5770R is a 6-channel, 14-bit resolution, low noise, programmable current output, digital-to-analog converter (DAC) for photonics control applications. The device incorporates a 1.25 V, on-chip voltage reference, a 2.5 k $\Omega$  precision resistor for reference current generation, die temperature, output monitoring functions, fault alarm, and reset functions.

The AD5770R contains five 14-bit resolution current sourcing DAC channels and one 14-bit resolution current sourcing and sinking DAC channel.

Channel 0 can be configured to sink up to 60 mA and source up to 300 mA. Channel 1 to Channel 5 have multiple programmable output current sourcing ranges set by register access.

Each DAC operates with a wide power supply rail from 0.8 V to AVDD – 0.4 V for optimizing power efficiency and thermal power dissipation.

The AD5770R operates from a 2.9 V to 5.5 V AVDD supply and is specified over the −40°C to +105°C temperature range.

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

**Data Sheet**

# **TABLE OF CONTENTS**

| Features                                    | 1  | Load DAC                               | 28 |

|---------------------------------------------|----|----------------------------------------|----|

| Applications                                | 1  | Input Page Mask Register               |    |

| General Description                         |    | DAC Page Mask Register                 |    |

| Functional Block Diagram                    |    | Output Stages                          |    |

| Specifications                              |    | Output Filter                          |    |

| AC Performance Characteristics              |    | Output Current Scaling                 |    |

| Timing Specifications                       | 7  | Applications Information               |    |

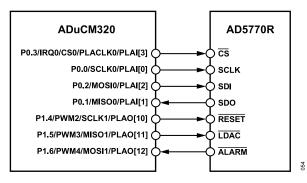

| Timing Diagrams                             |    | Microprocessor Interfacing             |    |

| Absolute Maximum Ratings                    |    | AD5770R to SPI Interface               |    |

| Thermal Resistance                          |    | Thermal Considerations                 | 33 |

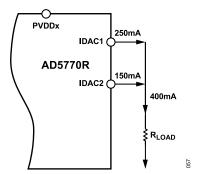

| ESD Caution                                 |    | Combining Channels to Increase Current |    |

| Pin Configuration and Function Descriptions | 10 | Range                                  | 33 |

| Typical Performance Characteristics         |    | Layout Guidelines                      |    |

| Terminology                                 |    | Register Summary                       |    |

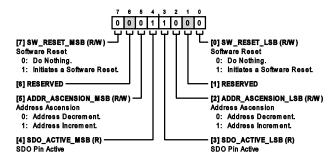

| Theory of Operation                         | 25 | SPI Configuration Registers            |    |

| Digital to Analog Converter                 |    | AD5770R Configuration Registers        |    |

| Precision Reference Current Generation      |    | Register Details                       |    |

| Diagnostic Monitoring                       |    | Outline Dimensions                     |    |

| Serial Interface                            |    | Ordering Guide                         | 61 |

| Reset Function                              | 28 | Evaluation Boards                      | 61 |

| REVISION HISTORY                            |    |                                        |    |

| 1/2023—Rev. A to Rev. B                     |    |                                        | _  |

|                                             |    |                                        |    |

| <u> </u>                                    |    |                                        |    |

| Changes to Address 0x44 Figure and Table 75 |    |                                        | 60 |

analog.com Rev. B | 2 of 61

# **SPECIFICATIONS**

AVDD = DVDD = 2.9 V to 5.5 V, PVDD = 0.8 V to AVDD - 0.4 V, AVEE = -3.0 V to 0 V,  $2.5 \text{ V} \leq \text{PVDD}$  - AVEE  $\leq 5.5 \text{ V}$ , IOVDD = 1.65 V to 5.5 V, AVEE  $\leq \text{PVEE0} \leq 0 \text{ V}$ , AVDD - PVEE0  $\leq 5.5 \text{ V}$ , VREF = 1.25 V external voltage reference, ambient temperature ( $T_A$ ) =  $-40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ , unless otherwise noted.

Table 1.

| Table 1.                                                   |      |     |       |              |                                                                                                |

|------------------------------------------------------------|------|-----|-------|--------------|------------------------------------------------------------------------------------------------|

| Parameter <sup>1</sup>                                     | Min  | Тур | Max   | Unit         | Test Conditions/Comments                                                                       |

| STATIC PERFORMANCE, EXTERNAL R <sub>SET</sub> <sup>2</sup> |      |     |       |              | VREF = 1.25 V external voltage reference, assumes                                              |

|                                                            |      |     |       |              | ideal 2.5 k $\Omega$ external R <sub>SET</sub> resistor, all channels and                      |

| D. J.C.                                                    |      |     |       | D.,          | all output current ranges                                                                      |

| Resolution                                                 | 14   |     |       | Bits         |                                                                                                |

| Relative Accuracy (INL)                                    | -6.5 |     | +6.5  | LSB          |                                                                                                |

| Differential Nonlinearity (DNL)                            | -1   |     | +1    | LSB          | T <sub>A</sub> = −20°C to +105°C, guaranteed monotonic                                         |

|                                                            | -1   |     | +1.2  | LSB          | Guaranteed monotonic                                                                           |

| Total Unadjusted Error                                     |      |     | 4.0   | % full-scale |                                                                                                |

| 7 0 1 5                                                    | -1.3 |     | +1.3  | range (FSR)  | 480 4 4 4 4 4 5 6 6 6 6                                                                        |

| Zero-Scale Error                                           |      |     | +600  | μA           | All 0s loaded into the DAC register                                                            |

| Zero-Scale Error Drift                                     |      | 500 |       | nA/°C        | Channel 0, Channel 1                                                                           |

|                                                            |      | 300 |       | nA/°C        | Channel 2                                                                                      |

|                                                            |      | 170 |       | nA/°C        | Channel 3, Channel 4, Channel 5                                                                |

| Offset Error                                               | -600 |     | +600  | μA           |                                                                                                |

| Offset Error Drift                                         |      | 1   |       | μΑ/°C        | Channel 0, Channel 1                                                                           |

|                                                            |      | 0.5 |       | μΑ/°C        | Channel 2, Channel 3, Channel 4, Channel 5                                                     |

| Full-Scale Error                                           | -1.3 |     | +1.3  | % FSR        | All 1s loaded into the DAC register                                                            |

| Full-Scale Error Drift                                     |      | 20  |       | ppm/°C       | Channel 0, Channel 1                                                                           |

|                                                            |      | 50  |       | ppm/°C       | Channel 2, Channel 3, Channel 4, Channel 5                                                     |

| Gain Error                                                 | -1.3 |     | +1.3  | % FSR        |                                                                                                |

| Gain Temperature Coefficient                               |      | 30  |       | ppm/°C       | Channel 0, Channel 1                                                                           |

|                                                            |      | 80  |       | ppm/°C       | Channel 2, Channel 3, Channel 4, Channel 5                                                     |

| DC Crosstalk                                               |      | 2   |       | LSB          | T <sub>A</sub> = 25°C, due to full-scale change in output current on a single adjacent channel |

| DC Power Supply Rejection Ratio (PSRR)                     |      | 17  |       | μA/V         | T <sub>A</sub> = 25°C, DAC register loaded to full scale                                       |

| STATIC PERFORMANCE, INTERNAL R <sub>SET</sub>              |      |     |       |              | VREF = 1.25 V internal voltage reference, all                                                  |

| ,                                                          |      |     |       |              | channels and all output current ranges                                                         |

| Resolution                                                 | 14   |     |       | Bits         |                                                                                                |

| Relative Accuracy (INL)                                    | -6.5 |     | +6.5  | LSB          |                                                                                                |

| Differential Nonlinearity (DNL)                            | -1   |     | +1    | LSB          | T <sub>A</sub> = −20°C to +105°C, guaranteed monotonic                                         |

|                                                            | -1   |     | +1.2  | LSB          | Guaranteed monotonic                                                                           |

| Total Unadjusted Error (TUE)                               | -1.3 |     | +1.3  | % FSR        |                                                                                                |

| Zero-Scale Error                                           |      |     | +600  | μA           | All 0s loaded into the DAC register                                                            |

| Zero-Scale Error Drift                                     |      | 500 |       | nA/°C        | Channel 0, Channel 1                                                                           |

|                                                            |      | 300 |       | nA/°C        | Channel 2                                                                                      |

|                                                            |      | 170 |       | nA/°C        | Channel 3, Channel 4, Channel 5                                                                |

| Offset Error                                               | -600 |     | +600  | μA           | , , , , , , , , , , , , , , , , , , , ,                                                        |

| Offset Error Drift                                         |      | 1   |       | μΑ/°C        | Channel 0, Channel 1                                                                           |

| Chock Eller Blik                                           |      | 0.5 |       | μΑ/°C        | Channel 2, Channel 3, Channel 4, Channel 5                                                     |

| Full-Scale Error                                           | -1.3 | 0.0 | +1.3  | % FSR        | All 1s loaded into the DAC register                                                            |

| Full-Scale Error Drift                                     | 1.0  | 20  | . 1.0 | ppm/°C       | Channel 0, Channel 1                                                                           |

| Tull-ocale Lift Difft                                      |      | 50  |       | ppm/°C       | Channel 2, Channel 3, Channel 4, Channel 5                                                     |

| Gain Error                                                 | -1.3 | 30  | +1.3  | % FSR        | Onamici 2, Onamici 3, Onamici 4, Onamici 3                                                     |

|                                                            | 1.0  | 20  | ۱.۵   |              | Channel 0, Channel 1                                                                           |

| Gain Temperature Coefficient                               |      | 30  |       | ppm/°C       |                                                                                                |

|                                                            |      | 80  |       | ppm/°C       | Channel 2, Channel 3, Channel 4, Channel 5                                                     |

analog.com Rev. B | 3 of 61

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter <sup>1</sup>                     | Min         | Тур  | Max              | Unit   | Test Conditions/Comments                                                                                         |

|--------------------------------------------|-------------|------|------------------|--------|------------------------------------------------------------------------------------------------------------------|

| DC Crosstalk                               |             | 2    |                  | LSB    | T <sub>A</sub> = 25°C, due to 200 mW change in output power of a single channel                                  |

| DC PSRR                                    |             | 17   |                  | μA/V   | T <sub>A</sub> = 25°C, DAC register loaded to midscale                                                           |

| OUTPUT CHARACTERISTICS                     |             |      |                  |        |                                                                                                                  |

| Output Current Ranges                      |             |      |                  |        |                                                                                                                  |

| Channel 0                                  | -60         |      | 0                | mA     |                                                                                                                  |

|                                            | -60         |      | +300             | mA     |                                                                                                                  |

|                                            | 0           |      | 300              | mA     |                                                                                                                  |

| Channel 1                                  | 0           |      | 140              | mA     |                                                                                                                  |

|                                            | 0           |      | 250              | mA     |                                                                                                                  |

| Channel 2                                  | 0           |      | 55               | mA     |                                                                                                                  |

|                                            | 0           |      | 150              | mA     |                                                                                                                  |

| Channel 3, Channel 4, Channel 5            | 0           |      | 45               | mA     |                                                                                                                  |

|                                            | 0           |      | 100              | mA     |                                                                                                                  |

| Output Compliance Voltage <sup>3</sup>     |             |      |                  |        |                                                                                                                  |

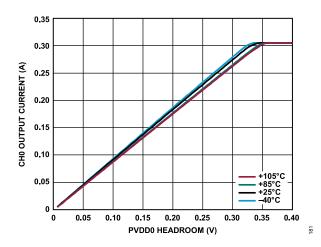

| Channel 0                                  | 0           |      | PVDD0 - 0.45     | V      | When sourcing in the 0 mA to 300 mA range, DAC register is loaded to full scale                                  |

|                                            | PVEE0 + 0.5 |      |                  |        | When sinking current on the -60 mA to 0 mA and the -60 mA to +300 mA ranges, DAC register is loaded t zero scale |

| Channel 1                                  | 0           |      | PVDD1 -<br>0.275 | V      | When configured to the 140 mA range with low headroom, DAC register is loaded to full scale                      |

|                                            | 0           |      | PVDD1 - 0.45     | V      | When configured to the 250 mA range or to the 140 mA range with low noise, DAC register is loaded to full scale  |

| Channel 2, Channel 3, Channel 4, Channel 5 | 0           |      | PVDDx -<br>0.275 | V      | All output ranges, DAC register loaded to full scale                                                             |

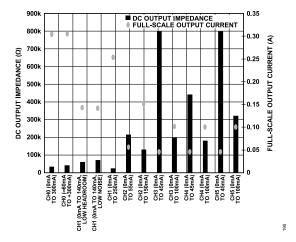

| DC Output Impedance                        |             | 600  |                  | kΩ     | T <sub>A</sub> = 25°C                                                                                            |

| OLTAGE REFERENCE INPUT                     |             |      |                  |        |                                                                                                                  |

| Reference Input Impedance                  |             | 60   |                  | GΩ     | T <sub>A</sub> = 25°C, external 1.25 V reference option                                                          |

|                                            |             | 115  |                  | kΩ     | T <sub>A</sub> = 25°C, external 2.5 V reference option                                                           |

| Reference Input Range                      |             | 1.25 |                  | V      | For specified performance, external 1.25 V reference option                                                      |

|                                            |             | 2.5  |                  | V      | External 2.5 V reference option                                                                                  |

| OLTAGE REFERENCE OUTPUT                    |             |      |                  |        |                                                                                                                  |

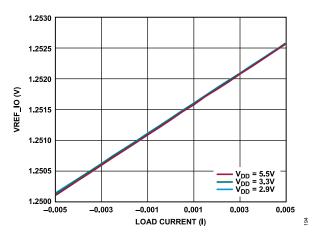

| Output Voltage                             | 1.245       | 1.25 | 1.255            | V      | T <sub>A</sub> = 25°C, reference output on                                                                       |

| Reference Temperature Coefficient          |             | 15   |                  | ppm/°C | Internal R <sub>SET</sub> resistor                                                                               |

| Output Impedance                           |             | 0.01 |                  | Ω      |                                                                                                                  |

| Output Current Load Capability             |             | ±5   |                  | mA     |                                                                                                                  |

| Maximum Capacitive Load                    |             | 10   |                  | μF     |                                                                                                                  |

| Load Regulation Sourcing                   |             | 250  |                  | μV/mA  |                                                                                                                  |

| Load Regulation Sinking                    |             | 250  |                  | μV/mA  |                                                                                                                  |

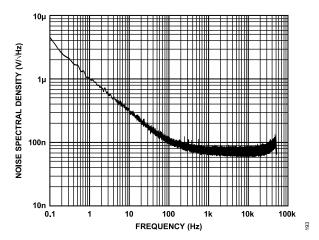

| Output Voltage Noise                       |             | 920  |                  | nV rms | T <sub>A</sub> = 25°C, 0.1 Hz to 10 Hz                                                                           |

| Output Voltage Noise Spectral Density      |             | 70   |                  | nV/√Hz | T <sub>A</sub> = 25°C , 1 kHz                                                                                    |

|                                            |             | 70   |                  | nV/√Hz | T <sub>A</sub> = 25°C, 10 kHz                                                                                    |

| Line Regulation                            |             | 35   |                  | μV/V   | T <sub>A</sub> = 25°C, due to change in AVDD                                                                     |

| NTEGRATED MULTIPLEXER                      |             |      |                  |        |                                                                                                                  |

| Buffer Output Current                      |             | ±8   |                  | mA     |                                                                                                                  |

| Buffer Output Impedance                    |             | 0.5  |                  | Ω      |                                                                                                                  |

| Buffer Offset                              |             | 0.3  |                  | mV     |                                                                                                                  |

analog.com Rev. B | 4 of 61

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter <sup>1</sup>                 | Min         | Тур  | Max         | Unit     | Test Conditions/Comments                                                  |

|----------------------------------------|-------------|------|-------------|----------|---------------------------------------------------------------------------|

| Buffer Maximum Capacitive Load         |             | 100  |             | pF       |                                                                           |

| LOGIC INPUTS                           |             |      |             | <u>'</u> | CS, SCLK, SDI, LDAC, RESET                                                |

| Input Current                          | -3.5        |      | +3.5        | μA       | Per pin                                                                   |

| Input Voltage                          |             |      |             |          |                                                                           |

| Input Low Voltage (V <sub>INL</sub> )  |             |      | 0.3 × IOVDD | V        |                                                                           |

| Input High Voltage (V <sub>INH</sub> ) | 0.7 × IOVDD |      |             | V        |                                                                           |

| Pin Capacitance                        |             | 4.5  |             | pF       | Per pin                                                                   |

| LOGIC OUTPUTS                          |             |      |             |          | ·                                                                         |

| SDO Pin                                |             |      |             |          |                                                                           |

| Output Low Voltage (V <sub>OL</sub> )  |             |      | 0.4         | V        |                                                                           |

| Output High Voltage (V <sub>OH</sub> ) | IOVDD - 0.4 |      |             | V        |                                                                           |

| Floating State Output Capacitance      |             | 4    |             | pF       |                                                                           |

| ALARM Pin                              |             |      |             |          |                                                                           |

| Output Low Voltage (V <sub>OL</sub> )  |             |      | 0.4         | V        | Open-drain enabled <sup>4</sup> , 10 kΩ pull-up resistor to IOVDE         |

| Output High Voltage (V <sub>OH</sub> ) | IOVDD – 0.4 |      | 0.1         | V        | Open-drain enabled <sup>4</sup> , 10 k $\Omega$ pull-up resistor to IOVDE |

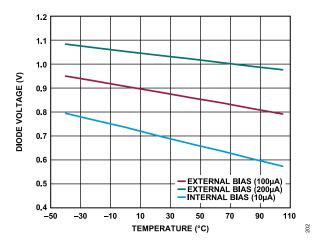

| TEMPERATURE MEASUREMENT DIODE          | 10122 0.1   |      |             | •        | open drain enabled , to the pain up resister to 10 VBB                    |

| Diode Output Voltage                   |             | 700  |             | mV       | T <sub>A</sub> = 25°C, internal bias current                              |

| Diode Output Voltage                   |             | 880  |             | mV       | $T_A = 25^{\circ}$ C, 100 µA external bias current                        |

|                                        |             | 1.04 |             | V        | $T_A = 25^{\circ}$ C, 200 $\mu$ A external bias current                   |

| Temperature Coefficient                |             | -1.8 |             | mV/°C    | Internal bias current                                                     |

| Temperature openiolent                 |             | -1.3 |             | mV/°C    | 100 µA external bias current                                              |

|                                        |             | -0.9 |             | mV/°C    | 200 µA external bias current                                              |

| External Bias Current <sup>5</sup>     | 100         | 0.0  | 200         | μA       | Temperature diode bias current is supplied externally                     |

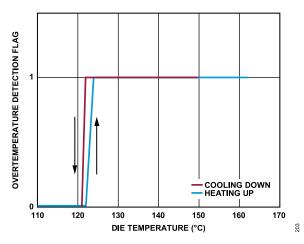

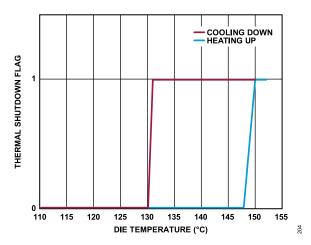

| THERMAL ALARMS                         | 100         |      | 200         | μ, ,     | Tomporatare aloae slac carron to cappilea externally                      |

| Overheat Warning Temperature           |             | 125  |             | °C       | Junction temperature, warning flag activated                              |

| Overheat Shutdown Temperature          |             | 150  |             | .c       | Junction temperature, thermal shutdown                                    |

| Overheat Warning Hysteresis            |             | 4    |             | .c       | danatan tamparatara, tramiar anataami                                     |

| Overheat Shutdown Hysteresis           |             | 20   |             | .c       |                                                                           |

| POWER REQUIREMENTS                     |             |      |             |          |                                                                           |

| Analog Power Supply Voltage            |             |      |             |          |                                                                           |

| AVDD                                   | 2.9         |      | 5.5         | V        | AVDD must be equal to DVDD                                                |

| AVEE                                   | -3.0        |      | 0           | V        | AVDD Illust be equal to DVDD                                              |

| PVDD0 to PVDD5                         | 0.8         |      | AVDD - 0.4  | V        | 2.5 V ≤ PVDD - AVEE ≤ 5.5 V                                               |

| PVEE0                                  | AVEE        |      | 0           | V        | AVDD - PVEE0 ≤ 5.5 V                                                      |

|                                        | AVEL        |      | U           | V        | AVDD 1 VEED 2 0.0 V                                                       |

| Analog Power Supply Current            |             | 20   |             | A        | Internal voltage reference oution coloated                                |

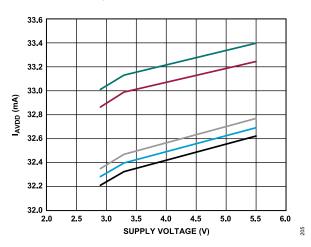

| AVDD Supply Current                    |             | 32   |             | mA       | Internal voltage reference option selected                                |

| AVEE Supply Current                    |             | -16  |             | mA       |                                                                           |

| PVDD0 to PVDD5 Supply Current          |             | 125  |             | μA       |                                                                           |

| Digital Power Supply Voltage           |             |      |             |          | N/DD 1/ 5//55                                                             |

| DVDD                                   | 2.9         |      | 5.5         | V        | AVDD must be equal to DVDD                                                |

| IOVDD                                  | 1.65        |      | 5.5         | V        |                                                                           |

| Digital Power Supply Current           |             |      |             |          |                                                                           |

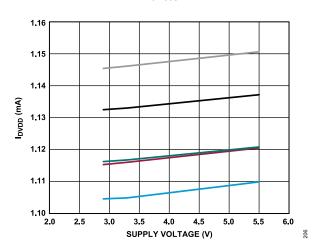

| DVDD Supply Current                    |             | 1.1  |             | mA       |                                                                           |

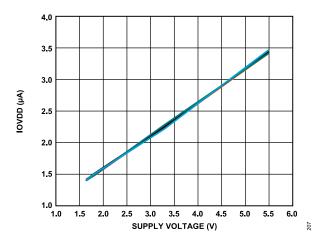

| IOVDD Supply Current                   |             | 200  |             | nA       |                                                                           |

| Power Consumption                      |             | 110  |             | mW       | All outputs at 0 A, nominal supplies                                      |

<sup>&</sup>lt;sup>1</sup> See the Terminology section.

analog.com Rev. B | 5 of 61

# **SPECIFICATIONS**

- See the Precision RSET Resistor section for more information about the internal and external R<sub>SET</sub> resistors.

- When sourcing current, the output compliance voltage is the maximum voltage at the IDACx pin, for which the output current is within 0.1% of the measured full-scale range. When sinking current on Channel 0, the output compliance voltage is the minimum voltage at the IDAC0 pin, for which the output current is within 0.1% of the measured zero-scale current.

- $^4$   $\,$  The active low  $\overline{\text{ALARM}}$  pin can be configured as an open drain. Refer to the ALARM section.

- <sup>5</sup> The internal temperature sensing diode can be biased with an internal or external current. Refer to the Internal Die Temperature Monitoring section.

### **AC PERFORMANCE CHARACTERISTICS**

AVDD = DVDD = 2.9 V to 5.5 V, PVDD = 0.8 V to AVDD - 0.4 V, AVEE = -3.0 V to 0 V,  $2.5 \text{ V} \le \text{PVDD}$  - AVEE  $\le 5.5 \text{ V}$ , IOVDD = 1.65 V to 5.5 V, AVEE  $\le \text{PVEE0} \le 0 \text{ V}$ , AVDD - PVEE0  $\le 5.5 \text{ V}$ , VREF = 1.25 V external voltage reference,  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted.

Table 2.

| Parameter <sup>1</sup>              | Min | Тур   | Max | Unit   | Test Conditions/Comments <sup>2</sup>                                                                      |

|-------------------------------------|-----|-------|-----|--------|------------------------------------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE                 |     |       |     |        |                                                                                                            |

| Output Current Settling Time        |     | 13    |     | μs     | Zero-scale to full-scale step settling to ±4 LSB, 0 mA to 300 mA range                                     |

|                                     |     | 10    |     | μs     | Zero-scale to full-scale step settling to ±4 LSB, 0 mA to 45 mA range, Channel 3, Channel 4, and Channel 5 |

| Slew Rate                           |     | 50    |     | mA/µs  | Channel 0 , 0 mA to 300 mA range                                                                           |

|                                     |     | 10    |     | mA/µs  | Channel 3, Channel 4, Channel 5, 0 mA to 45 mA range                                                       |

| Digital-to-Analog Glitch Impulse    |     | 0.057 |     | nA-sec | 1 LSB change around major carry                                                                            |

| Multiplexer Switching Glitch        |     | 14    |     | pA-sec | Switching monitored channel                                                                                |

| Digital Feedthrough                 |     | 0.03  |     | nA-sec |                                                                                                            |

| Digital Crosstalk                   |     | 0.03  |     | nA-sec |                                                                                                            |

| DAC-to-DAC Crosstalk                |     | 0.8   |     | nA-sec | Victim Channel 4, due to a 300 mA step change on Channel 0                                                 |

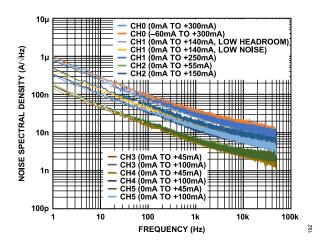

| Output Noise Spectral Density (NSD) |     | 35    |     | nA/√Hz | Channel 0, 0 mA to 300 mA range, at 1 kHz, DAC register loaded to midscale                                 |

|                                     |     | 18    |     | nA/√Hz | Channel 1, 0 mA to 140 mA low noise range, at 1 kHz, DAC register loaded to midscale                       |

|                                     |     | 19    |     | nA/√Hz | Channel 2, 0 mA to 150 mA range, at 1 kHz, DAC register loaded to midscale                                 |

|                                     |     | 13    |     | nA/√Hz | Channel 3, Channel 4, Channel 5, 0 mA to 100 mA range, at 1 kHz, DAC register loaded to midscale           |

|                                     |     | 16    |     | nA/√Hz | Channel 0, 0 mA to 300 mA range, at 10 kHz, DAC register loaded to midscale                                |

|                                     |     | 9     |     | nA/√Hz | Channel 1, 0 mA to 140 mA low noise range, at 10 kHz, DAC register loaded to midscale                      |

|                                     |     | 9     |     | nA/√Hz | Channel 2, 0 mA to 150 mA range, at 10 kHz, DAC register loaded to midscale                                |

|                                     |     | 6     |     | nA/√Hz | Channel 3, Channel 4, Channel 5, 0 mA to 100 mA range, at 10 kHz, DAC register loaded to midscale          |

| Output Noise                        |     | 900   |     | nA rms | 0.1 Hz to 10 Hz, Channel 0, 0 mA to 300 mA range, DAC register loaded to full scale                        |

|                                     |     | 180   |     | nA rms | 0.1 Hz to 10 Hz, Channel 1, 0 mA to 140 mA low noise range, DAC register loaded to full scale              |

|                                     |     | 400   |     | nA rms | 0.1 Hz to 10 Hz, Channel 2, 0 mA to 150 mA range, DAC register loaded to full scale                        |

|                                     |     | 300   |     | nA rms | 0.1 Hz to 10 Hz, Channel 3, Channel 4, Channel 5, 0 mA to 100 mA range, DAC register loaded to full scale  |

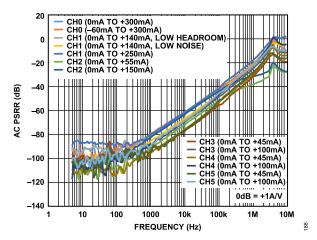

| PVDDx AC PSRR                       |     | -98   |     | dB     | 100 Hz                                                                                                     |

|                                     |     | -87   |     | dB     | 1 kHz                                                                                                      |

|                                     |     | -67   |     | dB     | 10 kHz                                                                                                     |

analog.com Rev. B | 6 of 61

# **SPECIFICATIONS**

### Table 2. (Continued)

| Parameter <sup>1</sup> | Min | Тур | Max | Unit | Test Conditions/Comments <sup>2</sup> |

|------------------------|-----|-----|-----|------|---------------------------------------|

|                        |     | -23 |     | dB   | 1000 kHz                              |

|                        |     | -8  |     | dB   | 3000 kHz                              |

<sup>&</sup>lt;sup>1</sup> See the Terminology section.

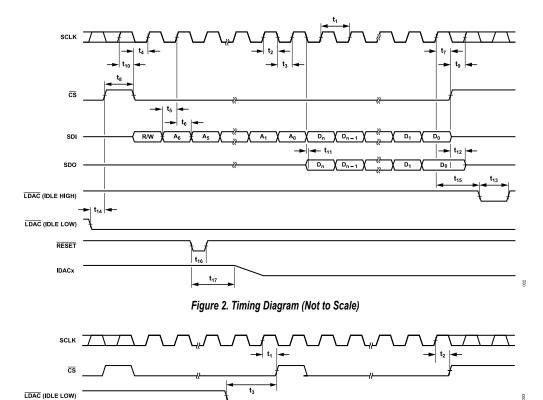

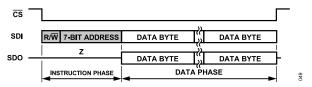

# **TIMING SPECIFICATIONS**

Table 3.

| Parameter         | 1.65 V ≤ IOVDD ≤ 5.5 V | Unit    | Test Conditions/Comments                                                     |

|-------------------|------------------------|---------|------------------------------------------------------------------------------|

| f <sub>SCLK</sub> | 20                     | MHz max | SCLK frequency, write operation.                                             |

|                   | 10                     | MHz max | SCLK frequency, read operation.                                              |

| $t_1$             | 50                     | ns min  | SCLK cycle time, write operation.                                            |

|                   | 100                    | ns min  | SCLK cycle time, read operation.                                             |

| $t_2$             | 20                     | ns min  | SCLK high time.                                                              |

| $t_3$             | 20                     | ns min  | SCLK low time.                                                               |

| $t_4$             | 25                     | ns min  | CS to SCLK rising edge setup time.                                           |

| $t_5$             | 10                     | ns min  | Data setup time.                                                             |

| $t_6$             | 10                     | ns min  | Data hold time.                                                              |

| t <sub>7</sub>    | 0                      | ns min  | SCLK rising edge to $\overline{\text{CS}}$ rising edge. LDAC idle high mode. |

| $t_7^1$           | 250                    | ns min  | SCLK rising edge to $\overline{\text{CS}}$ rising edge. LDAC idle low mode.  |

| t <sub>8</sub>    | 30                     | ns min  | CS high time.                                                                |

| $t_9$             | 40                     | ns min  | CS rising edge to SCLK rising edge.                                          |

| t <sub>10</sub>   | 5                      | ns min  | SCLK rising edge to $\overline{\text{CS}}$ falling edge.                     |

| t <sub>11</sub>   | 90                     | ns max  | SDO data valid from SCLK falling edge.                                       |

| t <sub>12</sub>   | 40                     | ns min  | CS rising edge to SDO disabled.                                              |

| t <sub>13</sub>   | 100                    | ns min  | LDAC pulse width low.                                                        |

| t <sub>14</sub>   | 10                     | ns min  | LDAC falling edge to CS rising edge.                                         |

| t <sub>15</sub>   | 100                    | ns min  | SCLK rising edge to LDAC falling edge.                                       |

| t <sub>16</sub>   | 10                     | ns min  | RESET minimum pulse width low.                                               |

| t <sub>17</sub>   | 100                    | ns max  | RESET pulse activation time.                                                 |

<sup>&</sup>lt;sup>1</sup>  $t_7$  ≥ 250 ns only applies to the first SCLK rising edge to  $\overline{CS}$  rising edge after  $\overline{LDAC}_{(IDLE\ LOW)}$  falling edge.  $t_7$  ≥ 0 ns applies for all other SCLK rising edge to  $\overline{CS}$  rising edge. Refer to Figure 3.

Table 4. LDAC Idle Low Timing

| Parameter      | 1.65 V ≤ IOVDD ≤ 5.5 V | Unit   | Test Conditions/Comments                                                                                                                                                       |

|----------------|------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>1</sub> | 250                    | ns min | SCLK rising edge to $\overline{\text{CS}}$ rising edge. The first SCLK rising edge to $\overline{\text{CS}}$ rising edge after $\overline{\text{LDAC}}$ idle low falling edge. |

| $t_2$          | 0                      | ns min | SCLK rising edge to $\overline{\text{CS}}$ rising edge.                                                                                                                        |

| t <sub>3</sub> | 10                     | ns min | LDAC falling edge to CS rising edge.                                                                                                                                           |

analog.com Rev. B | 7 of 61

$<sup>^2</sup>$  Temperature range is –40°C to +105°C, typically at 25°C.

# **SPECIFICATIONS**

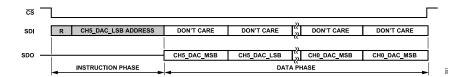

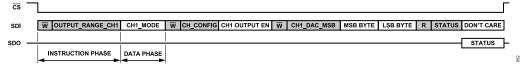

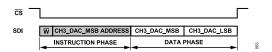

# **TIMING DIAGRAMS**

Figure 3. LDAC Idle Low Timing Diagram

analog.com Rev. B | 8 of 61

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 5.

| Parameter                                       | Rating                         |

|-------------------------------------------------|--------------------------------|

| AVDD to DVDD                                    | -0.3 V to +0.3 V               |

| AVDD to AGND                                    | -0.3 V to +6.5 V               |

| AVDD to PVDDx                                   | -0.3 V to +6.5 V               |

| AVDD to AVEE                                    | -0.3 V to +10 V                |

| AVEE to AGND                                    | +0.3 V to -3.5 V               |

| PVEE0 to AGND                                   | +0.3 V to -3.5 V               |

| AVEE to PVEE0                                   | -3 .0 V to +0.3 V              |

| PVDDx to AGND                                   | -0.3 V to +6.5 V               |

| PVDDx to AVEE                                   | -0.3 V to +8.5 V               |

| AVDD to PVEE0                                   | -0.3 V to +6.5 V               |

| VREF_IO to AGND                                 | -0.3 V to AVDD + 0.3 V         |

| IDAC0 to PVEE0                                  | -0.3 V to +6.5 V               |

| IDAC1 through IDAC5 to AGND                     | -0.3 V to PVDDx + 0.3 V        |

| DVDD to DGND                                    | -0.3 V to +6.5 V               |

| IOVDD to DGND                                   | -0.3 V to +6.5 V               |

| REFGND to AGND                                  | -0.3 V to +0.3 V               |

| AGND to DGND                                    | -0.3 V to +0.3 V               |

| Digital Inputs to DGND <sup>1</sup>             | -0.3 V to IOVDD + 0.3 V        |

| Digital Outputs to DGND <sup>2</sup>            | -0.3 V to IOVDD + 0.3 V        |

| Operating Temperature Range                     | -40°C to +105°C                |

| Storage Temperature Range                       | -65°C to +150°C                |

| Maximum Junction Temperature, T <sub>JMAX</sub> | 150°C                          |

| Power Dissipation                               | $(T_{JMAX} - T_A)/\theta_{JA}$ |

|                                                 | 260°C, as per JEDEC            |

| Lead Temperature, Soldering Reflow              | J-STD-020                      |

<sup>&</sup>lt;sup>1</sup> Digital inputs include SCLK, SDI, RESET, and LDAC.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.

Table 6. Thermal Resistance

| Package Type | $\theta_{JA}$   | Unit |

|--------------|-----------------|------|

| CB-49-5      | 30 <sup>1</sup> | °C/W |

<sup>1</sup> Thermal impedance simulated values are based on JEDEC 2S2P thermal test board with 16 thermal vias. See JEDEC JESD51.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. B | 9 of 61

Digital outputs include SDO and ALARM.

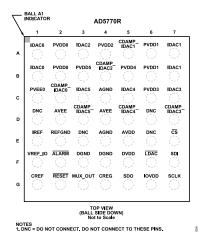

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

Table 7. Pin Function Descriptions

| Pin No.        | Mnemonic    | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                          |

|----------------|-------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, B1         | IDAC0       | AO                | Current Output of Channel 0 is Available on this Pin. Channel 0 sinks up to 60 mA and sources up to 300 mA.                                                                                                                                                                                          |

| A2, B2         | PVDD0       | S                 | Power Supply for IDAC0.                                                                                                                                                                                                                                                                              |

| A3             | IDAC2       | AO                | Current Output of Channel 2 is Available on this Pin. Channel 2 sources up to 150 mA.                                                                                                                                                                                                                |

| A4             | PVDD2       | S                 | Power Supply for IDAC2.                                                                                                                                                                                                                                                                              |

| A5             | CDAMP_IDAC1 | Al                | Damping Capacitor for IDAC1. Connect a 10 nF capacitor between this pin and the PVDD1 supply.                                                                                                                                                                                                        |

| A6, B6         | PVDD1       | s                 | Power Supply for IDAC1.                                                                                                                                                                                                                                                                              |

| A7, B7         | IDAC1       | AO                | Current Output of Channel 1 is Available on this Pin. Channel 1 sources up to 250 mA.                                                                                                                                                                                                                |

| B3             | PVDD5       | S                 | Power Supply for IDAC5.                                                                                                                                                                                                                                                                              |

| B4             | CDAMP_IDAC2 | Al                | Damping Capacitor for IDAC2. Connect a 10 nF capacitor between this pin and the PVDD2 supply.                                                                                                                                                                                                        |

| B5             | PVDD4       | S                 | Power Supply for IDAC4.                                                                                                                                                                                                                                                                              |

| C1             | PVEE0       | S                 | Power Supply Return for IDAC0 Sink. When sinking this current on Channel 0, up to 60 mA flows out of PVEE0.                                                                                                                                                                                          |

| C2             | CDAMP_IDAC0 | Al                | Damping Capacitor for IDAC0. Connect a 10 nF capacitor between this pin and the PVDD0 supply.                                                                                                                                                                                                        |

| C3             | IDAC5       | AO                | Current Output of Channel 5 is Available on this Pin. Channel 5 sources up to 100 mA.                                                                                                                                                                                                                |

| C4, E4         | AGND        | S                 | Analog Supply Ground Pin.                                                                                                                                                                                                                                                                            |

| C5             | IDAC4       | AO                | Current Output of Channel 4 is Available on this Pin. Channel 4 sources up to 100 mA.                                                                                                                                                                                                                |

| C6             | PVDD3       | s                 | Power Supply for IDAC3.                                                                                                                                                                                                                                                                              |

| C7             | IDAC3       | AO                | Current Output of Channel 3 is Available on this Pin. Channel 3 sources up to 100 mA.                                                                                                                                                                                                                |

| D1, D6, E3, E6 | DNC         | DNC               | Do Not Connect. Do not connect to this pin.                                                                                                                                                                                                                                                          |

| D2, D4         | AVEE        | S                 | Negative Power Supply. AVEE must be between -3 V and 0 V. This pin supplies the low side voltage for biasing some analog circuit blocks.                                                                                                                                                             |

| D3             | CDAMP_IDAC5 | Al                | Damping Capacitor for IDAC5. Connect a 10 nF capacitor between this pin and the PVDD5 supply.                                                                                                                                                                                                        |

| D5             | CDAMP_IDAC4 | Al                | Damping Capacitor for IDAC4. Connect a 10 nF capacitor between this pin and the PVDD4 supply.                                                                                                                                                                                                        |

| D7             | CDAMP_IDAC3 | Al                | Damping Capacitor for IDAC3. Connect a 10 nF capacitor between this pin and the PVDD3 supply.                                                                                                                                                                                                        |

| E1             | IREF        | AI/O              | External Resistor Pin for Reference Current Generation (Optional). When using an external $R_{SET}$ resistor, connect this pin directly to REFGND via a low drift, 2.5 k $\Omega$ external resistor.                                                                                                 |

| E2             | REFGND      | S                 | Reference Supply Ground Pin. Connect this pin with a low impedance path to AGND. If using an external resistor, the low side of the R <sub>SET</sub> resistor must be connected to REFGND before the connection to AGND.                                                                             |

| E5             | AVDD        | S                 | Analog Power Supply. AVDD must be between 2.9 V and 5.5 V. This pin supplies power to the analog circuit blocks on the device. This pin must be at the same potential as DVDD.                                                                                                                       |

| E7             | CS          | DI                | Active Low Control Input. $\overline{\text{CS}}$ is used to frame data during a SPI transaction. When $\overline{\text{CS}}$ is low, data is transferred on the rising edges of SCLK.                                                                                                                |

| F1             | VREF_IO     | AI/O              | Voltage Reference Input/Output. When the internal reference is enabled, the buffered 1.25 V reference voltage can be made available on this pin. When the internal reference is disabled, an external reference must be applied to this pin. The external reference voltage must be 1.25 V or 2.5 V. |

analog.com Rev. B | 10 of 61

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 7. Pin Function Descriptions (Continued)

| Pin No. | Mnemonic | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                          |

|---------|----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F2      | ALARM    | DO                | Active Low Output. When ALARM goes low, this alerts the user of a change in the status register. User must read the status register to deassert this pin.                                                                                                                            |

| F3, F4  | DGND     | S                 | Digital Power Supply Ground.                                                                                                                                                                                                                                                         |

| F5      | DVDD     | S                 | Digital Power Supply. DVDD must be between 2.9 V and 5.5 V. This pin supplies power to the digital core and internal oscillator blocks on the device. This pin must be at the same potential as AVDD.                                                                                |

| F6      | LDAC     | DI                | Logic Input. Pulsing this pin low allows any or all DAC registers to be updated if the input registers have new data, allowing any or all DAC outputs to update synchronously. Alternatively, this pin can be tied low.                                                              |

| F7      | SDI      | DI                | Serial Data Input. Data to be written to the device is provided on this input and is clocked into the register on the rising edge of SCLK.                                                                                                                                           |

| G1      | CREF     | AI/O              | Filter Capacitor for Voltage Reference. A 0.1 µF capacitor connected from the CREF pin to AGND is recommended to achieve the specified performance from the AD5770R.                                                                                                                 |

| G2      | RESET    | DI                | Active Low Reset Input. Tie this pin high for normal operation. Asserting this pin low resets the AD5770R to the default configuration.                                                                                                                                              |

| G3      | MUX_OUT  | AI/O              | Analog Output. An external analog-to-digital converter (ADC) reads voltages on this pin for diagnostic purposes. Use external excitation current for the temperature sensing diode and force the current on this pin.                                                                |

| G4      | CREG     | AI/O              | Filter Capacitor for Internal Regulator. A 1 $\mu$ F capacitor connected from the CREG pin to AGND is recommended to achieve the specified performance from the AD5770R.                                                                                                             |

| G5      | SDO      | DO                | Serial Data Output. A read back operation provides data on this output pin as a serial data stream. Data is clocked out on the falling edge of SCLK and is valid on the rising edge of SCLK.                                                                                         |

| G6      | IOVDD    | S                 | Logic Power Supply. IOVDD must be between 1.65 V and 5.5 V. This pin supplies power to the serial interface circuit blocks on the device.                                                                                                                                            |

| G7      | SCLK     | DI                | Serial Clock Input. Data is clocked into the input shift register on the rising edge of the serial clock input. Data can be transferred at rates up to 20 MHz when writing to the AD5770R. This pin has a maximum speed of 10 MHz when performing a read operation from the AD5770R. |

AO is analog output, S is power, AI is analog input, DNC is do not connect, AI/O is analog input and output, DI is digital input, and DO is digital output.

analog.com Rev. B | 11 of 61

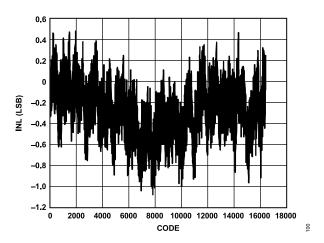

# TYPICAL PERFORMANCE CHARACTERISTICS

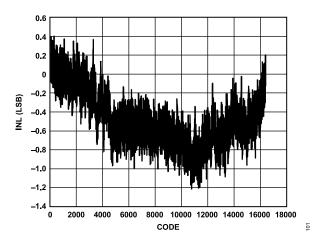

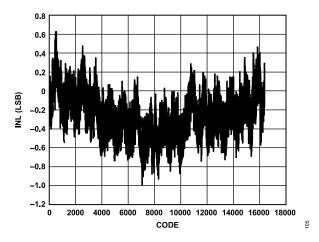

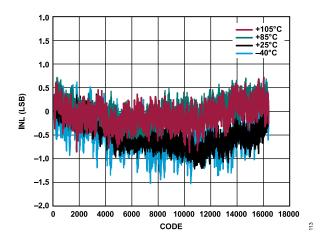

Figure 5. INL Error vs. DAC Code (Channel 0, 0 mA to 300 mA Range)

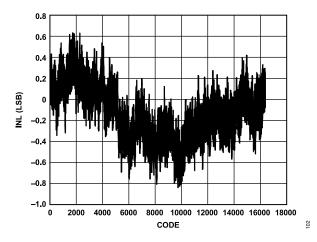

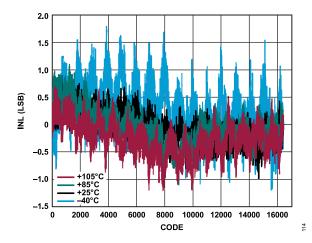

Figure 6. INL Error vs. DAC Code (Channel 1, 0 mA to 250 mA Range)

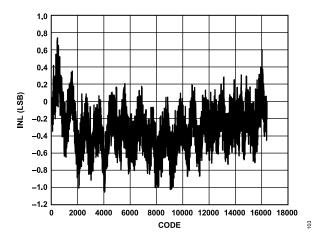

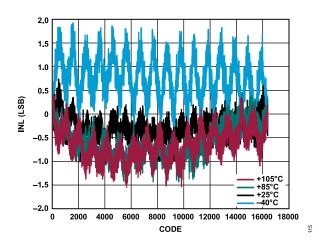

Figure 7. INL Error vs. DAC Code (Channel 2, 0 mA to 150 mA Range)

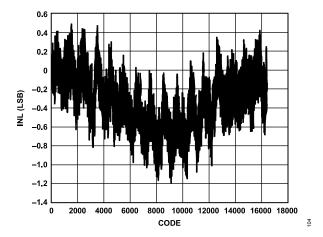

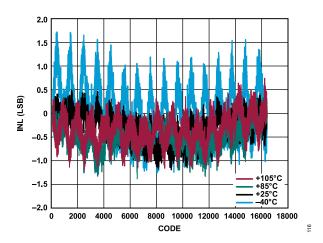

Figure 8. INL Error vs. DAC Code (Channel 3, 0 mA to 100 mA Range)

Figure 9. INL Error vs. DAC Code (Channel 4, 0 mA to 100 mA Range)

Figure 10. INL Error vs. DAC Code (Channel 5, 0 mA to 100 mA Range)

analog.com Rev. B | 12 of 61

### TYPICAL PERFORMANCE CHARACTERISTICS

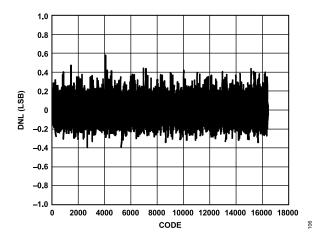

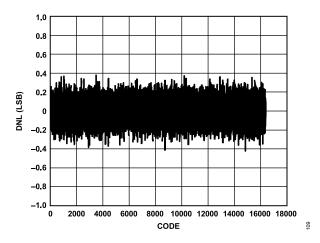

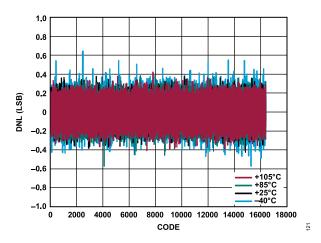

Figure 11. DNL Error vs. DAC Code (Channel 0, 0 mA to 300 mA Range)

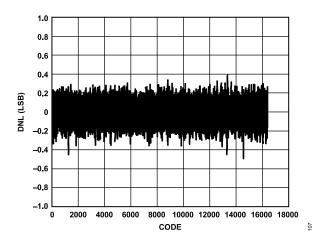

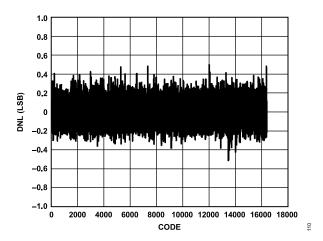

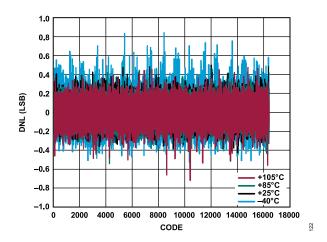

Figure 12. DNL Error vs. DAC Code (Channel 1, 0 mA to 250 mA Range)

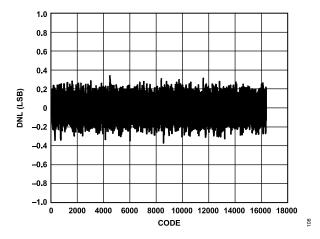

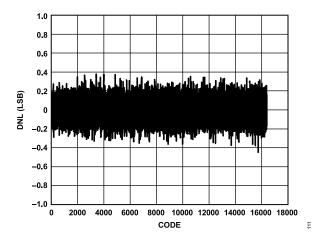

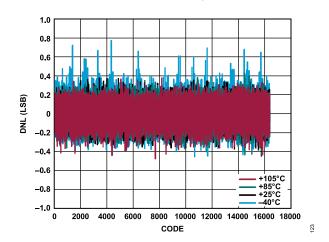

Figure 13. DNL Error vs. DAC Code (Channel 2, 0 mA to 150 mA Range)

Figure 14. DNL Error vs. DAC Code (Channel 3, 0 mA to 100 mA Range)

Figure 15. DNL Error vs. DAC Code (Channel 4, 0 mA to 100 mA Range)

Figure 16. DNL Error vs. DAC Code (Channel 5, 0 mA to 100 mA Range)

analog.com Rev. B | 13 of 61

# TYPICAL PERFORMANCE CHARACTERISTICS

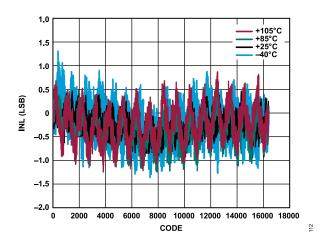

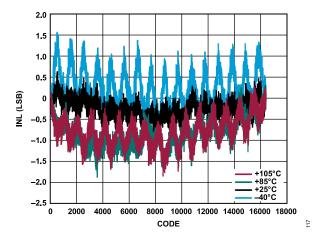

Figure 17. INL Error vs. DAC Code for Various Temperatures (Channel 0, 0 mA to 300 mA Range)

Figure 18. INL Error vs. DAC Code for Various Temperatures (Channel 1, 0 mA to 250 mA Range)

Figure 19. INL Error vs. DAC Code for Various Temperatures (Channel 2, 0 mA to 150 mA Range)

Figure 20. INL Error vs. DAC Code for Various Temperatures (Channel 3, 0 mA to 100 mA Range)

Figure 21. INL Error vs. DAC Code for Various Temperatures (Channel 4, 0 mA to 100 mA Range)

Figure 22. INL Error vs. DAC Code for Various Temperatures (Channel 5, 0 mA to 100 mA Range)

analog.com Rev. B | 14 of 61

# TYPICAL PERFORMANCE CHARACTERISTICS

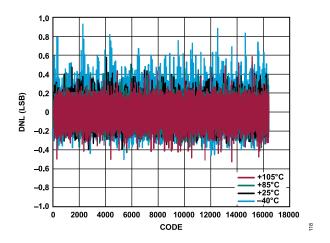

Figure 23. DNL Error vs. DAC Code for Various Temperatures (Channel 0, 0 mA to 300 mA Range)

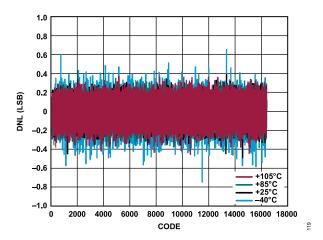

Figure 24. DNL Error vs. DAC Code for Various Temperatures (Channel 1, 0 mA to 250 mA Range)

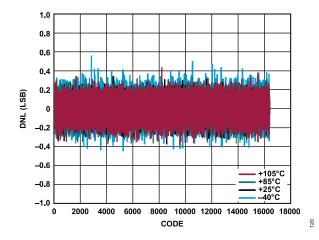

Figure 25. DNL Error vs. DAC Code for Various Temperatures (Channel 2, 0 mA to 150 mA Range)

Figure 26. DNL Error vs. DAC Code for Various Temperatures (Channel 3, 0 mA to 100 mA Range)

Figure 27. DNL Error vs. DAC Code for Various Temperatures (Channel 4, 0 mA to 100 mA Range)

Figure 28. DNL Error vs. DAC Code for Various Temperatures (Channel 5, 0 mA to 100 mA Range)

analog.com Rev. B | 15 of 61

# TYPICAL PERFORMANCE CHARACTERISTICS

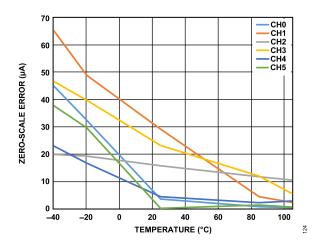

Figure 29. Zero-Scale Error vs. Temperature

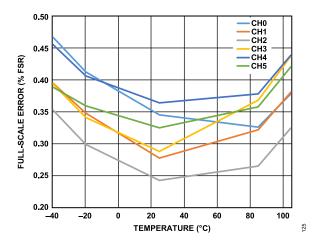

Figure 30. Full-Scale Error vs. Temperature

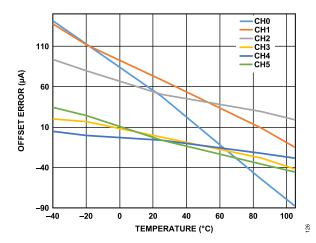

Figure 31. Offset Error vs. Temperature

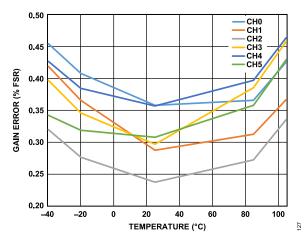

Figure 32. Gain Error vs. Temperature

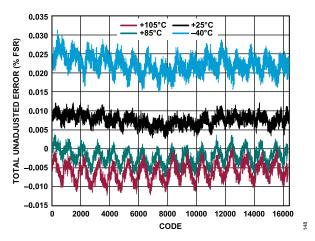

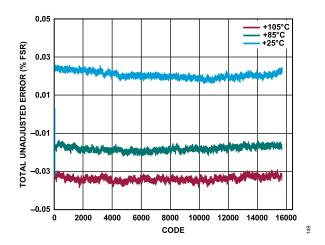

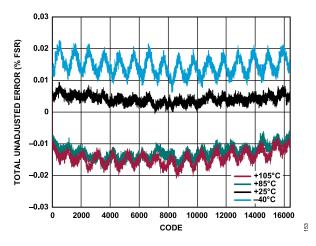

Figure 33. Total Unadjusted Error vs. DAC Code for Various Temperatures (Channel 0, 0 mA to 300 mA Range)

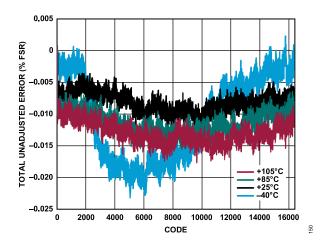

Figure 34. Total Unadjusted Error vs. DAC Code for Various Temperatures (Channel 1, 0 mA to 250 mA Range)

analog.com Rev. B | 16 of 61

### TYPICAL PERFORMANCE CHARACTERISTICS

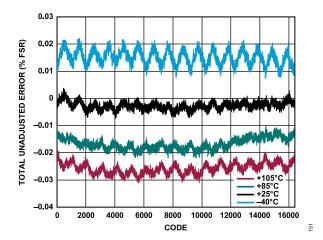

Figure 35. Total Unadjusted Error vs. DAC Code for Various Temperatures (Channel 2, 0 mA to 150 mA Range)

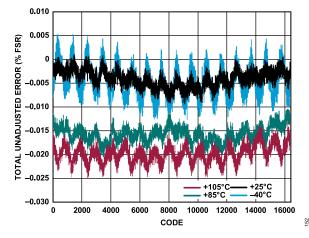

Figure 36. Total Unadjusted Error vs. DAC Code for Various Temperatures (Channel 3, 0 mA to 100 mA Range)

Figure 37. Total Unadjusted Error vs. DAC Code for Various Temperatures (Channel 4, 0 mA to 100 mA Range)

Figure 38. Total Unadjusted Error vs. DAC Code for Various Temperatures (Channel 5, 0 mA to 100 mA Range)

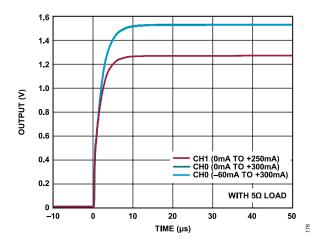

Figure 39. Full-Scale Settling Time (Rising Step)

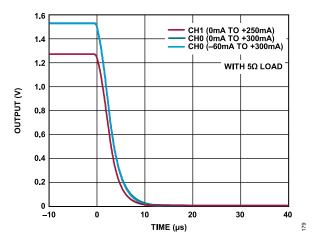

Figure 40. Full-Scale Settling Time (Falling Step)

analog.com Rev. B | 17 of 61

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 41. CH0 Output Current vs. PVDD0 Headroom for Various Temperatures

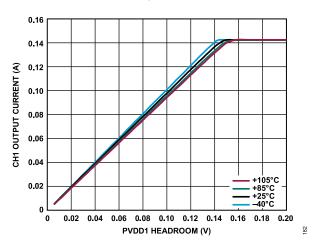

Figure 42. CH1 Output Current vs. PVDD1 Headroom for Various Temperatures

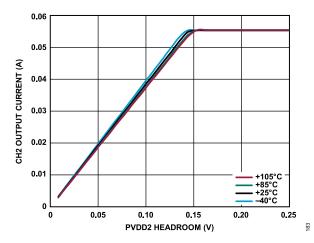

Figure 43. CH2 Output Current vs. PVDD2 Headroom for Various Temperatures

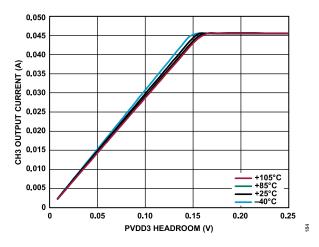

Figure 44. CH3 Output Current vs. PVDD3 Headroom for Various Temperatures

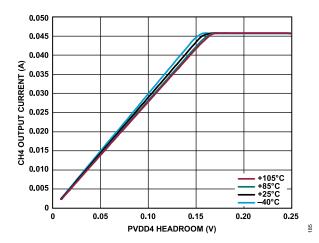

Figure 45. CH4 Output Current vs. PVDD4 Headroom for Various Temperatures

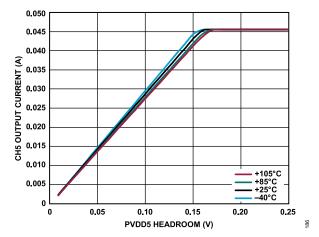

Figure 46. CH5 Output Current vs. PVDD5 Footroom for Various Temperatures

analog.com Rev. B | 18 of 61

# TYPICAL PERFORMANCE CHARACTERISTICS

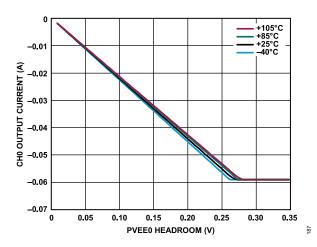

Figure 47. CH0 Output Current vs. PVEE0 Footroom for Various Temperatures

Figure 48. AC PSRR vs. Frequency (All Ranges)

Figure 49. DC Output Impedance vs. Full-Scale Output Current (All Ranges)

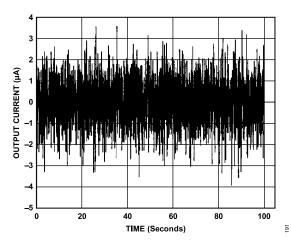

Figure 50. Peak-to-Peak Noise, 0.1 Hz to 10 Hz Bandwidth, (CH0 0 mA to 300 mA Range)

Figure 51. Output NSD vs. Frequency (All Ranges)

Figure 52. VREF\_IO Output NSD vs. Frequency

analog.com Rev. B | 19 of 61

### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 53. VREF\_IO Voltage vs. Load Current

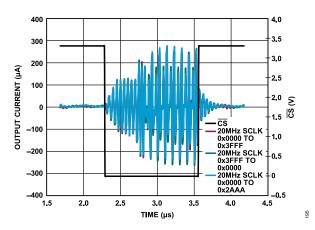

Figure 54. Digital Feedthrough

Figure 55. DAC to DAC Crosstalk (Victim Channel Zero)

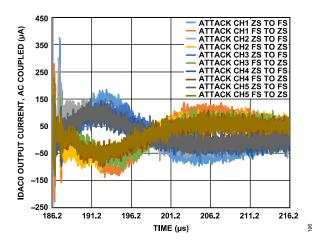

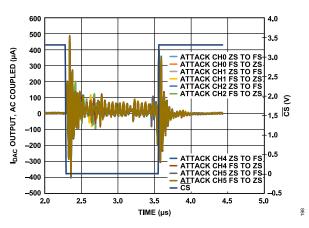

Figure 56. Analog Crosstalk

Figure 57. Digital Crosstalk

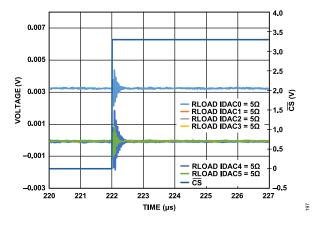

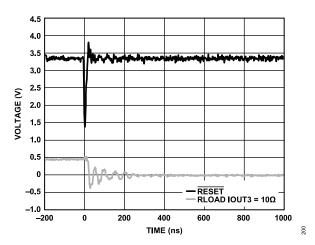

Figure 58. Reset Glitch

analog.com Rev. B | 20 of 61

# TYPICAL PERFORMANCE CHARACTERISTICS

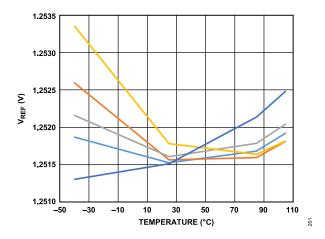

Figure 59. V<sub>REF</sub> vs. Temperature for Devices for Five AD5770R Devices

Figure 60. Diode Voltage vs. Temperature

Figure 61. Overheat Warning

Figure 62. Overheat Shutdown

Figure 63. AVDD Supply Current (I<sub>AVDD</sub>) vs. Supply Voltage for Five AD5770R Devices

Figure 64. DVDD Supply Current (I<sub>DVDD</sub>) vs. Supply Voltage for Five AD5770R

Devices

analog.com Rev. B | 21 of 61

# TYPICAL PERFORMANCE CHARACTERISTICS

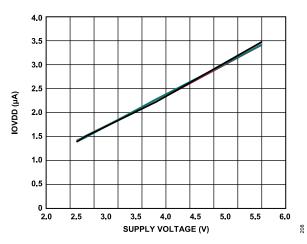

Figure 65. IOVDD Supply Current vs. IOVDD Supply Voltage for Five AD5770R Devices

Figure 66. IOVDD Supply Current vs. IOVDD Supply Voltage for Five AD5770R Devices

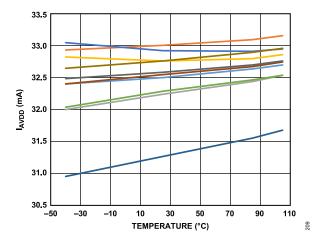

Figure 67. I<sub>AVDD</sub> vs. Temperature for Ten AD5770R Devices

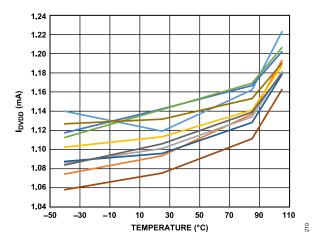

Figure 68. I<sub>DVDD</sub> vs. Temperature for Ten AD5770R Devices

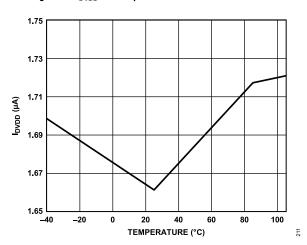

Figure 69. I<sub>DVDD</sub> vs. Temperature

analog.com Rev. B | 22 of 61

### **TERMINOLOGY**

#### **TUE**

Total unadjusted error is a measure of the output error taking all the various errors into account, namely INL error, offset error, gain error, and output drift over supplies, temperature, and time. TUE is expressed in % FSR.

# **Relative Accuracy or Integral Nonlinearity (INL)**

Relative accuracy or integral nonlinearity is a measurement of the maximum deviation, in LSBs, from a straight line passing through the endpoints of the DAC transfer function. Typical INL error vs. DAC code plots are shown in Figure 5 to Figure 10.

# **Differential Nonlinearity (DNL)**

Differential nonlinearity is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of ±1 LSB maximum ensures monotonicity. This DAC is guaranteed monotonic by design. Typical DNL error vs. DAC code plots are shown in Figure 11 to Figure 16.

### **Zero-Scale Error**

Zero-scale error is a measurement of the output error when zero code (0x0000) is loaded to the DAC register. Zero code error is expressed in  $\mu A$ .

# **Zero-Scale Error Temperature Coefficient**

Zero code error drift is a measure of the change in zero code error with a change in temperature. It is expressed in nA/°C.

#### **Gain Error**

Gain error is a measure of the span error of the DAC. It is the deviation in slope of the DAC transfer characteristic from the ideal expressed as % FSR.

### **Gain Error Temperature Coefficient**

Gain temperature coefficient is a measurement of the change in gain error with changes in temperature. It is expressed in ppm of FSR/°C.

#### Offset Error

Offset error is a measurement of the difference between  $I_{OUT}x$  (actual) and  $I_{OUT}x$  (ideal), expressed in  $\mu A$ , in the linear region of the transfer function. Offset error can be negative or positive.

### **Offset Error Drift**

Offset error drift is a measurement of the change in offset error with a change in temperature. It is expressed in  $\mu A \ ^{\circ} C$ .

# **DC Power Supply Rejection Ratio (PSRR)**

PSRR indicates how the output of the DAC is affected by changes in the supply voltage. PSRR is the ratio of the change in I<sub>OUT</sub>x to a

change in AVDD for a full-scale output of the DAC. It is measured in  $\mu$ A/V.

# **Output Settling Time**

Output settling time is the amount of time it takes for the output of a DAC to settle to a specified level for a zero-scale to full-scale input change and is measured from the falling edge of  $\overline{\text{LDAC}}$ .

# **Digital-to-Analog Glitch Impulse**

Digital-to-analog glitch impulse is the impulse injected into the analog output when the input code in the DAC register changes state. It is normally specified as the area of the glitch in nA-sec, and is measured when the digital input code is changed by 1 LSB at the major carry transition (0x1FFF to 0x2000 for the AD5770R).

# **Digital Feedthrough**

Digital feedthrough is a measure of the impulse injected into the analog output of the DAC from the digital inputs of the DAC, but is measured when the DAC output is not updated. It is specified in nA-sec and measured with a full-scale code change on the data bus, that is, from all 0s to all 1s and vice versa.

### **DC Crosstalk**

DC crosstalk is the dc change in the output level of one DAC in response to a change in the output of another DAC. It is measured with a full-scale output change on one DAC when monitoring another DAC maintained at midscale. It is expressed in nA-sec.

# **Digital Crosstalk**

Digital crosstalk is the glitch impulse transferred to the output of one DAC at midscale in response to a full-scale code change (all 0s to all 1s and vice versa) in the input register of another DAC. It is measured in standalone mode and is expressed in nA-sec.

### **DAC to DAC Crosstalk**

DAC to DAC crosstalk is the glitch impulse transferred to the output of one DAC due to a digital code change and subsequent analog output change of another DAC. It is measured by loading the attack channel with a full-scale code change (all 0s to all 1s and vice versa), using the write to and update commands when monitoring the output of the victim channel that is at midscale. The energy of the glitch is expressed in nA-sec.

# **Output Noise Spectral Density**

Output noise spectral density is a measurement of the internally generated random noise. Random noise is characterized as a spectral density (nA/ $\sqrt{Hz}$ ). It is measured by loading the DAC to midscale and measuring noise at the output. It is measured in nA/ $\sqrt{Hz}$ .

analog.com Rev. B | 23 of 61

# **TERMINOLOGY**

# **Multiplexer Switching Glitch**

The multiplexer switching glitch is a measure of the impulse injected into the analog output of the DAC when the monitor mux is changed to monitor a different channel.

# **AC Power Supply Rejection Ratio (AC PSRR)**

AC power supply rejection ratio is a measure of the rejection of the output current to ac changes in the power supplies applied to the DAC. AC PSRR is measured for a given amplitude and frequency change in power supply voltage and is expressed in decibels.

analog.com Rev. B | 24 of 61

#### THEORY OF OPERATION

#### DIGITAL TO ANALOG CONVERTER

The AD5770R is a 6-channel, 14-bit, serial input, current output DAC capable of multiple low noise output current ranges with high power efficiency. Each of the six DACs has a segmented current steering architecture, chosen to achieve low glitch performance when changing codes.

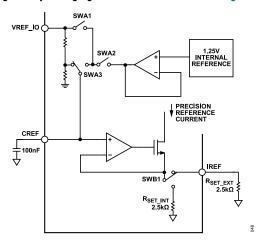

# PRECISION REFERENCE CURRENT GENERATION

The AD5770R requires a 500  $\mu$ A precision reference current for all four DAC cores, which is generated using a 1.25 V voltage reference and a 2.5 k $\Omega$  precision R<sub>SET</sub> resistor. The AD5770R integrates an internal 1.25 V voltage reference and 2.5 k $\Omega$  internal precision R<sub>SET</sub> resistor for this function. The AD5770R can also use an external voltage reference and external precision R<sub>SET</sub> resistor for the reference current generation. Ensure that the voltage reference and the precision R<sub>SET</sub> resistor have low noise, high accuracy, and low temperature drift to help minimize the overall IDACx gain error and gain error drift. Table 1 outlines the performance specifications of the AD5770R with both the internal reference and internal R<sub>SET</sub> resistor, and an external 1.25 V reference and external precision R<sub>SET</sub> resistor.

# Voltage Reference

The AD5770R can use an external voltage reference for the precision reference current generation. The external reference voltage can be either 1.25 V or 2.5 V, configured by writing to the REFERENCE\_VOLTAGE\_SEL bits in the reference register. When the user selects the 2.5 V external voltage reference option, an internal voltage divider attenuates to achieve the 1.25 V required.

The device powers up with the external 2.5 V reference voltage option selected.

The AD5770R integrates a low noise, on-chip, 15 ppm/°C, 1.25 V voltage reference that can be used as the voltage reference. The on-chip reference is powered down by default and is enabled when the REFERENCE\_VOLTAGE\_SEL bits in the reference register select the internal reference.

The buffered 1.25 V internal reference voltage can be made available at the VREF IO pin for use as a system reference.

Regardless of the voltage reference scheme used, it is recommended that a 100 nF capacitor is placed between the CREF pin and AGND to achieve specified performance. A simplified diagram of the voltage reference configuration is shown in Figure 70.

When the internal 1.25 V reference is selected and made available on the VREF\_IO pin, switch SWA1 and switch SWA2 are closed, and switch SWA3 is connected to switch SWA2.

When the internal 1.25 V reference is selected but not made available on the VREF\_IO pin, switch SWA1 is open, switch SWA2 is closed, and switch SWA3 is connected to switch SWA2.

When the external 1.25 V reference option is selected, switch SWA1 is closed, switch SWA2 is open, and switch SWA3 is connected to switch SWA2.

When the external 2.5 V option is selected, switch SWA1 and switch SWA2 are open and switch SWA3 is connected to the resistor divider shown in Figure 70.

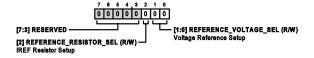

# Precision R<sub>SFT</sub> Resistor

The AD5770R integrates an on-chip  $2.5~k\Omega$  (10 ppm/°C, 0.1%) precision  $R_{SET}$  resistor that can be used for the reference current generation. If required, an external precision  $R_{SET}$  resistor can be used for reference current generation. The user selects an internal or an external reference resistor by writing to the REFERENCE\_RESISTOR\_SEL bit in the reference register. The AD5770R powers up with the internal precision  $R_{SET}$  resistor selected.

The AD5770R integrates fault protection circuitry when using an external resistor. The AD5770R automatically switches from an external to an internal resistor if the external resistor option is selected, and if the external resistance is below the minimum specification. A simplified diagram of the how the reference resistor is configured by changing switch SWB1 is shown in Figure 70.

Figure 70. AD5770R Reference Options

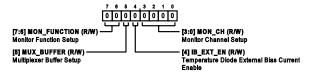

### **DIAGNOSTIC MONITORING**

The AD5770R diagnostic feature allows the user to monitor output compliance voltages, output currents, and the internal die temperature of the device. The output compliance voltages, which are voltages representative of output current and internal die temperature, are multiplexed on-chip and are available on the MUX\_OUT pin and can be measured using an external ADC.

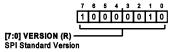

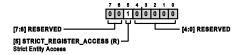

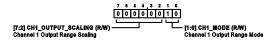

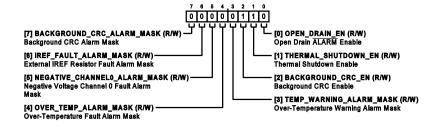

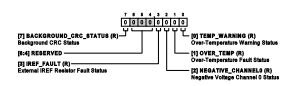

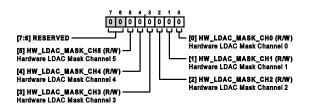

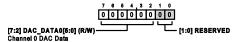

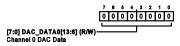

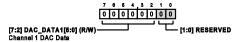

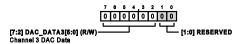

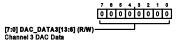

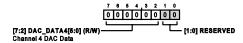

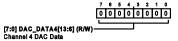

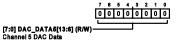

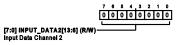

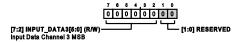

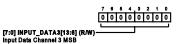

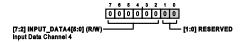

Diagnostics monitoring is disabled on power up and can be enabled by writing to the MON\_FUNCTION bits in the MONITOR\_SETUP register.