001

# Dual-, Differential, Low-Pass Filter µModule with Gain and ADC Driver

### **FEATURES**

- Dual-channel differential input/output

- Integrated 36 MHz, 8-pole low-pass filter

- Low power dissipation

- 213 mW typical at 3 V supply

- 2 integrated fully differential ADC drivers

- 30 dB maximum differential gain

- Adjustable down to 14 dB

- Gain error: ±0.2 dB

- ▶ Gain drift: 0.01 dB/°C typical

- 2.7 V to 3.3 V supply range

- ▶ 84-ball, 6 mm × 12 mm CSP BGA package with 0.8 mm ball pitch

- ► Operating temperature range: -40°C to +85°C

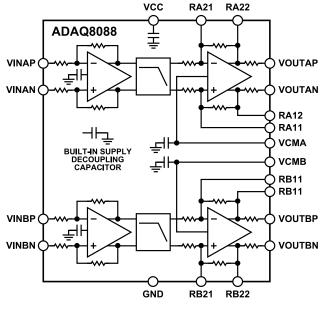

- Built-in supply decoupling capacitors

### **APPLICATIONS**

- IF broadband demodulators

- Medical imaging (CW ultrasound beam forming)

- Phased array systems

- Radar

- Adaptive antennas

- Communications receivers

- Radio Links

- Wireless local loop

- RF instrumentation

- Satellite modems

- Baseband data acquisition system

- Multichannel digitizer instruments

- Ultrasonic non-destructive test

### **GENERAL DESCRIPTION**

The ADAQ8088 is a dual-channel analog system in package (SIP) that integrates three common signal processing and conditioning blocks to support a variety of demodulator applications and data acquisition applications. The device integrates all active and passive components to form a complete signal chain between the output of an I/Q demodulator and the input to an analog-to-digital converter (ADC). The device also forms the complete signal chain between a transducer output and the input to an ADC in baseband data acquisition systems. No external components are required for proper functionality.

Each channel contains a preamplifier, followed by an 8-pole, lowpass filter with a 36 MHz, 3 dB frequency, and a differential ADC driver optimized to drive 12-bit to 14-bit pipeline ADCs with speeds Rev. C

**TECHNICAL SUPPORT**

FUNCTIONAL BLOCK DIAGRAM

up to 150 MSPS. Encapsulated in a 6 mm × 12 mm CSP BGA package, the ADAQ8088 minimizes space requirements in high density multichannel systems.

The ADAQ8088 operating temperature range is from -40°C to +85°C.

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog DOCUMENT FEEDBACK Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features                                     | 1 |

|----------------------------------------------|---|

| Applications                                 | 1 |

| Functional Block Diagram                     | 1 |

| General Description                          | 1 |

| Specifications                               | 3 |

| Absolute Maximum Ratings                     | 4 |

| Thermal Resistance                           | 4 |

| ESD Caution                                  | 4 |

| Pin Configurations and Function Descriptions | 5 |

| Typical Performance Characteristics          | 6 |

| Theory of Operation                          | 9 |

| Circuit Information                          |   |

|                                              |   |

| Input Resistance            | 9  |

|-----------------------------|----|

| Low Pass Filter             | 9  |

| Noise                       | 9  |

| Output Stage                | 9  |

| Resolution                  | 9  |

| Power Supply Decoupling     | 9  |

| Gain                        | 9  |

| Applications Information    | 11 |

| Typical Application Circuit | 11 |

| Outline Dimensions          | 13 |

| Ordering Guide              | 13 |

| Evaluation Boards           |    |

|                             |    |

### **REVISION HISTORY**

| 9/2023—Rev. B to Rev. C                        | 0  |

|------------------------------------------------|----|

| Changes to Gain Section.                       | 9  |

| Changes to Typical Application Circuit Section | 11 |

| 8/2022—Rev. A to Rev. B                        |    |

| Change to Figure 20                            | 9  |

| Changes to Evaluation Boards                   |    |

| 2/2022—Rev. 0 to Rev. A                        |    |

| Added Noise Figure Parameter, Table 1          | 3  |

| Added Figure 13; Renumbered Sequentially       |    |

### 2/2021—Revision 0: Initial Version

## **SPECIFICATIONS**

VCC = 3.0 V, common-mode voltage ( $V_{CM}$ ) floating, VINAP, VINAN, VINBP, and VINBN are self biased, differential 63 mV p-p input at 1 MHz,  $T_A = 25^{\circ}$ C, unless otherwise noted.

| Parameter                                    | Test Conditions/Comments                                        | Min | Тур   | Max  | Unit    |

|----------------------------------------------|-----------------------------------------------------------------|-----|-------|------|---------|

| INPUT CHARACTERISTICS                        |                                                                 |     |       |      |         |

| Input Impedance                              | Each input to GND                                               |     | 249/1 |      | Ω/pF    |

| Open Circuit Voltage at V <sub>IN</sub> Pins | VCC = 2.7 V                                                     |     | 1.15  |      | V dc    |

|                                              | VCC = 3.0 V                                                     |     | 1.25  |      | V dc    |

|                                              | VCC = 3.3 V                                                     |     | 1.38  |      | V dc    |

| Input Current                                | Each input to GND, VCC = 2.7 V                                  |     | -550  |      | μA      |

| input outlont                                | VCC = 3.0 V                                                     |     | -610  |      | μΑ      |

|                                              | VCC = 3.3 V                                                     |     | -670  |      | μΑ      |

| Input Offset Current                         | Each input to GND, VCC = 2.7 V                                  |     | ±3.5  |      | μΑ      |

| Input Onset Current                          | VCC = 3.0 V                                                     |     | ±4.0  |      |         |

|                                              |                                                                 |     |       |      | μΑ      |

|                                              | VCC = 3.3 V                                                     |     | ±4.5  | 1/00 | μA      |

| Input Common-Mode Voltage Range              |                                                                 | GND |       | VCC  | V       |

| Differential RTI Vos                         | Each input to GND, maximum = average + $4\delta$                |     | +0.7  |      | mV      |

| V <sub>OS</sub> Drift                        | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                   |     | 7.5   |      | μV/°C   |

| DYNAMIC CHARACTERISTICS                      |                                                                 |     |       |      |         |

| Bandwidth                                    | $V_{OUT}$ = 2 V p-p differential, R <sub>L</sub> = 1 k $\Omega$ |     | 36    |      | MHz     |

| Bandwidth Drift                              | $T_A = -40^{\circ}C$ to $+85^{\circ}C$                          |     | 0.1   |      | MHz/°C  |

| Slew Rate                                    |                                                                 |     | 180   |      | V/µs    |

| Differential Gain                            | With no external resistors                                      |     | 30    |      | dB      |

| Gain Error                                   | Channel to channel, at 10 MHz                                   |     | ±0.2  |      | dB      |

| Gain Drift                                   | $T_A = -40^{\circ}C$ to $+85^{\circ}C$                          |     | 0.01  |      | dB/°C   |

| Phase Match Error                            | Channel to channel, at 10 MHz                                   |     | 0.5   |      | Degrees |

| OUTPUT CHARACTERISTICS                       |                                                                 |     |       |      |         |

| Output Voltage                               |                                                                 |     |       |      |         |

| High                                         | $R_L$ = 806 Ω, either output pin                                |     | 2.15  |      | V       |

| Low                                          | $R_{L} = 806 \Omega$ , either output pin                        |     | 0.17  |      | V       |

| Output Short-Circuit Current                 |                                                                 |     | 50    |      | mA      |

| Output Balance Error                         |                                                                 |     | -60   |      | dB      |

| Output Resistance                            | In series with each output                                      |     | 10    |      | Ω       |

| Crosstalk                                    |                                                                 |     | 80    |      | dB      |

|                                              |                                                                 |     | 00    |      |         |

|                                              | At 1 MHz                                                        |     | 7     |      | nV/√Hz  |

| RTI Voltage Noise Density                    |                                                                 |     | 7     |      |         |

|                                              | At 10 MHz                                                       |     | 6     |      | nV/√Hz  |

| RTO Voltage Noise Density                    | Gain = 30 dB, f = 1 MHz                                         |     | 220   |      | nV/√Hz  |

|                                              | Gain = 30 dB, f = 10 MHz                                        |     | 190   |      | nV/√Hz  |

| Noise Figure                                 | Gain = 30 dB, f = 20 MHz                                        |     | 13    |      | dB      |

| Total Harmonic Distortion (THD)              |                                                                 |     | -63   |      | dB      |

| 1/f Corner                                   |                                                                 |     | 20    |      | kHz     |

| CM CHARACTERISATICS                          |                                                                 |     |       |      |         |

| V <sub>CM</sub> Gain                         |                                                                 |     | 1     |      | V/V     |

| V <sub>CM</sub> Range                        |                                                                 | 0.5 |       | 2    | V       |

| V <sub>CM</sub> Input Resistance             |                                                                 |     | 18    |      | kΩ      |

| POWER SUPPLY                                 |                                                                 |     |       |      |         |

| Operating Range                              |                                                                 | 2.7 |       | 3.3  | V       |

| Quiescent Current                            |                                                                 |     | 71    | 88   | mA      |

| PSRR                                         |                                                                 |     | 70    |      | dB      |

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                             | Rating                              |

|---------------------------------------|-------------------------------------|

| Analog Inputs                         | 3.5 V                               |

| Supply Voltage                        | 3.5 V                               |

| Storage Temperature Range             | -55°C to +125°C                     |

| Junction Temperature                  | 150°C                               |

| Lead Temperature Soldering            | 260°C reflow as per JEDEC J-STD-020 |

| Electrostatic Discharge (ESD) Ratings | 500 V                               |

| Human Body Model (HBM)                | 2k V                                |

| Field Induced Charged Device Model    | 500 V                               |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

#### Table 3. Thermal Resistance

| Package           | θ <sub>JA</sub> | θ <sub>JC_TOP</sub> | θ <sub>ЈС_ВОТТОМ</sub> | θ <sub>JB</sub> | Ψ <sub>JT</sub> | Ψ <sub>JB</sub> |

|-------------------|-----------------|---------------------|------------------------|-----------------|-----------------|-----------------|

| Type <sup>1</sup> | (°C/W)          | (°C/W)              | (°C/W)                 | (°C/W)          | (°C/W)          | (°C/W)          |

| BC-84-4           | 33              | 21.1                | 12.2                   | 13.7            | 11              | 13              |

$^1~$  Test Condition 1: Thermal impedance simulated values are based on use of a 2S2P with vias JEDEC PCB excluding the  $\theta_{JC\_TOP}$ , which uses 1S0P JEDEC PCB.

Thermal resistance values specified in Table 3 are simulated based on JEDEC specifications (unless specified otherwise) and should be used in compliance with JESD51-12.

#### ESD CAUTION

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

002

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

|   | ADAQ8088<br>TOP VIEW<br>(Not to Scale) |     |     |     |     |     |     |     |      |     |     |      |      |        |

|---|----------------------------------------|-----|-----|-----|-----|-----|-----|-----|------|-----|-----|------|------|--------|

|   | 1                                      | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9    | 10  | 11  | 12   | 13   | 14     |

| Α | VINAP                                  | DNC | DNC | GND | DNC | DNC | GND | GND | VCMA | DNC | DNC | RA21 | RA22 | VOUTAP |

| в | GND                                    | GND | GND | GND | GND | GND | GND | GND | GND  | GND | GND | GND  | GND  | GND    |

| с | VINAN                                  | DNC | DNC | vcc | vcc | vcc | vcc | vcc | vcc  | vcc | DNC | RA11 | RA12 | VOUTAN |

| D | VINBP                                  | DNC | DNC | vcc | vcc | vcc | vcc | vcc | vcc  | vcc | DNC | RB11 | RB12 | VOUTBP |

| Е | GND                                    | GND | GND | GND | GND | GND | GND | GND | GND  | GND | GND | GND  | GND  | GND    |

| F | WINBN                                  | DNC | DNC | GND | DNC | DNC | GND | GND | VCMB | DNC | DNC | RB21 | RB22 | VOUTBN |

NOTES 1. DNC = DO NOT CONNECT.

### Figure 2. Pin Configuration

#### Table 4. Pin Function Descriptions

| Pin No.                                                                      | Mnemonic   | Type <sup>1</sup> | Description                                   |

|------------------------------------------------------------------------------|------------|-------------------|-----------------------------------------------|

| A1                                                                           | VINAP      | AI                | Analog Input for Channel A.                   |

| A2, A3, A5, A6, A10, A11, C2, C3, C11, D2, D3, D11, F2, F3, F5, F6, F10, F11 | DNC        | DNC               | Do Not Connect. Do not connect to these pins. |

| A4, A7, A8, B1 to B14, E1 to E14, F4, F7, F8                                 | GND        | Р                 | Analog Ground.                                |

| A9                                                                           | VCMA       | AI                | V <sub>CM</sub> Input from the ADC.           |

| A12, A13                                                                     | RA21, RA22 | AI                | External Resistors for Channel A.             |

| A14                                                                          | VOUTAP     | AO                | Analog Output for Channel A.                  |

| C1                                                                           | VINAN      | AI                | Analog Input for Channel A.                   |

| C4 to C10, D4 to D10                                                         | VCC        | Р                 | Power Supplies, 2.7 V to 3.3 V.               |

| C12, C13                                                                     | RA11, RA12 | AI                | External Resistors for Channel A.             |

| C14                                                                          | VOUTAN     | AO                | Analog Output for Channel A.                  |

| D1                                                                           | VINBP      | AI                | Analog Input for Channel B.                   |

| D12, D13                                                                     | RB11, RB12 | AI                | External Resistors for Channel B.             |

| D14                                                                          | VOUTBP     | AO                | Analog Output for Channel B.                  |

| F1                                                                           | VINBN      | AI                | Analog Input for Channel B.                   |

| F9                                                                           | VCMB       | AI                | V <sub>CM</sub> Input from the ADC.           |

| F12, F13                                                                     | RB21, RB22 | AI                | External Resistors for Channel B.             |

| F14                                                                          | VOUTBN     | AO                | Analog Output for Channel B.                  |

<sup>1</sup> Al is analog input, DNC is do not connect, P is power, and AO is analog output.

# **TYPICAL PERFORMANCE CHARACTERISTICS**

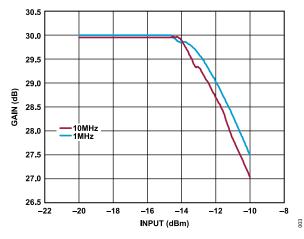

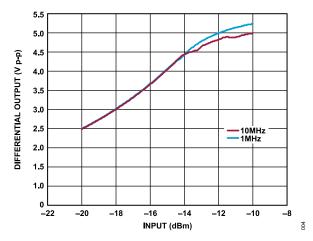

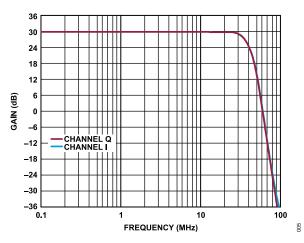

VCC = 3 V; V<sub>CM</sub> is floating, typically 1.25 V;  $R_{LOAD}$  = 1 k $\Omega$ ; T = 25°C, inputs and outputs are measured differentially, unless otherwise noted.

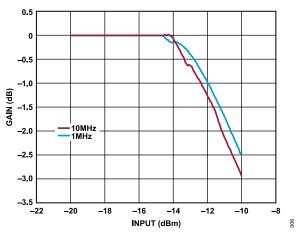

Figure 3. Gain vs. Input Power, Input Frequency at 1 MHz and 10 MHz

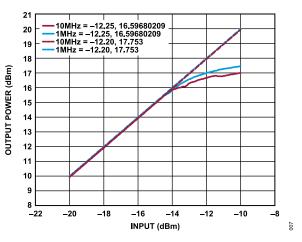

Figure 4. V<sub>OUT</sub> vs. Input Power with Gain Set to 30 dB, Input Frequency at 1 MHz and 10 MHz

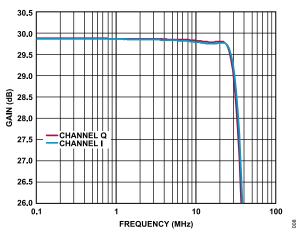

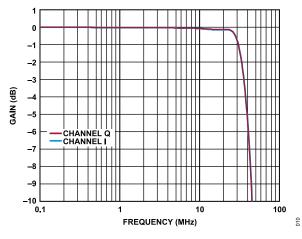

Figure 5. Frequency Response, Input = -20 dBm

Figure 6. Normalized Gain vs. Input Power, Input Frequency at 1 MHz and 10 MHz

Figure 7. 1 dB Gain Compression with Gain Set to 30 dB, Input Frequency at 1 MHz and 10 MHz

Figure 8. Gain Flatness, Input = -20 dBm

### **TYPICAL PERFORMANCE CHARACTERISTICS**

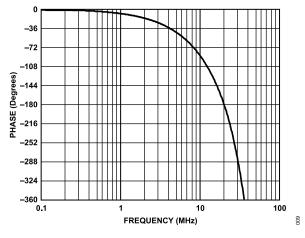

Figure 9. Phase Response with Gain Set to 30 dB, Input = -20 dBm

Figure 10. Normalized Frequency Response, Input = -20 dBm

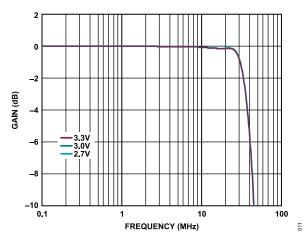

Figure 11. Frequency Response vs. Supply, Input = -20 dBm

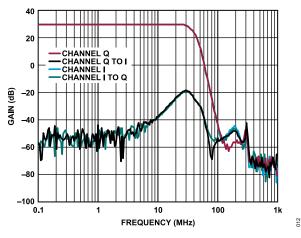

Figure 12. I/Q Channel Crosstalk

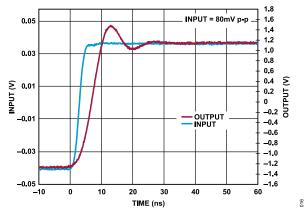

Figure 14. Step Response with Gain Set to 30 dB

-60

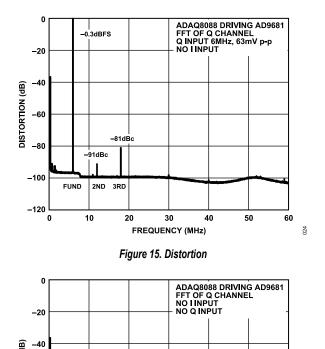

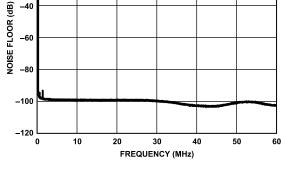

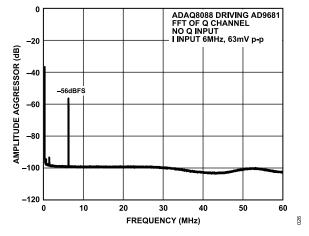

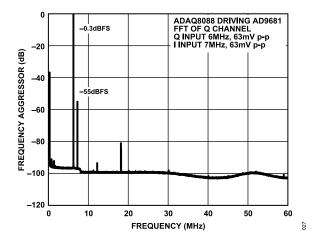

## **TYPICAL PERFORMANCE CHARACTERISTICS**

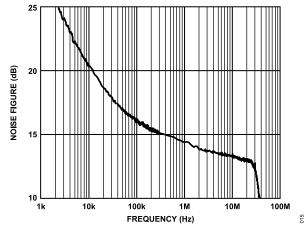

Figure 16. Noise Floor

025

Figure 17. Amplitude Aggressor

Figure 18. Frequency Aggressor

## THEORY OF OPERATION

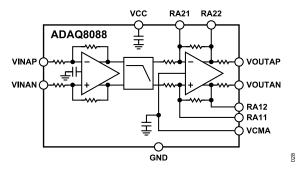

Figure 19. 1/2 ADAQ8088 Simplified Schematic

#### **CIRCUIT INFORMATION**

The ADAQ8088 system in package (SiP) is an analog signal chain designed to interface baseband I/Q from quadrature demodulators to 12-bit to 14-bit pipeline ADCs.

#### INPUT RESISTANCE

The equivalent input impedance of each input of the ADAQ8088 is a 249  $\Omega$  resistor connected to VCC/2.

Each baseband output of the demodulator is loaded with the input impedance of the ADAQ8088. To avoid saturating the ADAQ8088 inputs, ac couple demodulators with high dc bias on the I/Q outputs to the ADAQ8088.

### LOW PASS FILTER

An 8-pole Butterworth low-pass filter provides steep roll-off beyond the filter corner frequency of 36 MHz typical.

### NOISE

Input referred broad band noise density of the ADAQ8088 is

6 nV/√Hz

1/f corner is located at 20 kHz.

### **OUTPUT STAGE**

The output stage is optimized to drive 12-bit to 14-bit pipeline ADCs with speeds of 150 MSPS or lower.

The output resistance of the ADAQ8088 is set to  $10 \Omega$ . Additional resistors in series with each output and a differential capacitor placed as close to the ADC inputs as possible provides additional filtering.

DC bias of the outputs is set by the voltage on the VCMA pin and the VCMB pin. Floating these pins self adjusts the outputs to 1.25 V (internally biased). Additionally, these pins are typically connected to the chosen ADC  $V_{CM}$  output pin.

### RESOLUTION

Two 15  $\Omega$  resistors, each in series with an output pin of the ADAQ8088 and a 10 pF capacitor across the ADC input pins, allows just over a 10-bit effective resolution at full-scale input for an ADC with a 4 ns acquisition time.

The 190 nV/ $\sqrt{Hz}$  RTO noise density of the ADAQ8088 at a gain value of 30 dB, integrated over the 36 MHz signal bandwidth, allows an effective signal resolution of 9 bits which is suitable for a 10-bit ADC with 2 V p-p FS analog input.

Reducing the gain to 20 dB increases the effective resolution to 10.5 bits in an ADC with 2 V p-p FS analog input.

### POWER SUPPLY DECOUPLING

The ADAQ8088 features built in, 0.1  $\mu\text{F}$  supply decoupling capacitors on VCC.

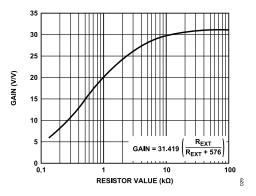

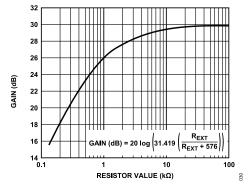

#### GAIN

With no external component, the gain of the ADAQ8088 is set to 30 dB. This gain can be reduced with external resistors ( $R_{EXT}$ ) connected between the following pins: RA11 and RA12, RA21 and RA22, RB11 and RB12, and RB21 and RB22.

The maximum gain is 30 dB with no resistors. The minimum gain is 14 dB when  $R_{EXT}$  = 110  $\Omega$ . Figure 20 shows the gain vs.  $R_{EXT}$  value.

Gain can be further reduced by a factor of 249/(249 + R) with external resistors connected in series with each input.

To guarantee stability, 1 pF capacitors must be added across Pin RA11 and Pin RA12, Pin RA21 and Pin RA22, Pin RB11 and Pin RB12, and Pin RB21 and Pin RB22.

Figure 20. Gain vs. External Resistor Value

### THEORY OF OPERATION

Figure 21. Gain (dB) vs. External Resistor Value

### **APPLICATIONS INFORMATION**

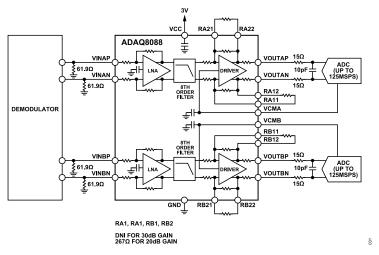

# TYPICAL APPLICATION CIRCUIT

Figure 22 shows an example of how the ADAQ8088 can be directly coupled to a demodulator. Place the 61.9  $\Omega$  resistors close to the ADAQ8088 input pins. The parallel combination of the resistors and the 249  $\Omega$  input impedance of the ADAQ8088 provides a 50  $\Omega$  termination for the demodulator outputs. If the ADC is located physically some distance from the ADAQ8088 and is driven with a transmission line, place the 40.2  $\Omega$  series resistors close to the ADAQ8088 output pins. These resistors, along with the device internal impedance, provide a 50  $\Omega$  series termination. The value

of the shunt capacitor, C, is dependent on the input frequency and may need to be reduced or removed.

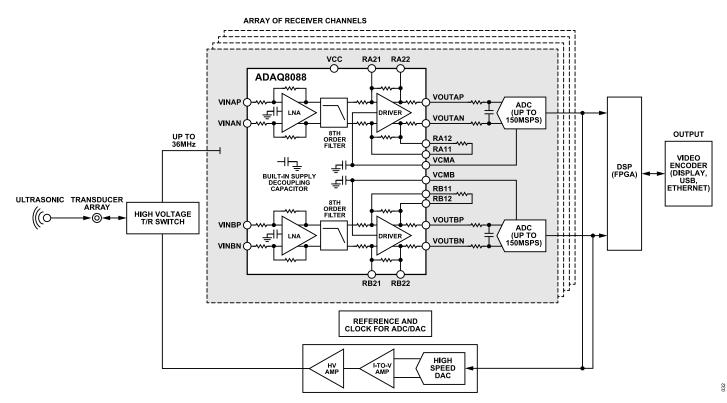

Figure 23 shows an example of how the ADAQ8088 can be used as part of an ultrasonic non-destructive test.

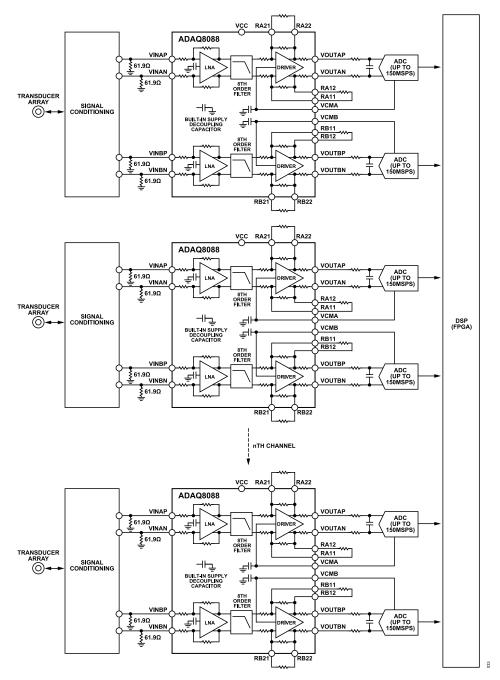

Figure 24 shows an example of how the ADAQ8088 works on high accuracy, wide bandwidth, multichannel digitizer instruments.

The 1 pF capacitors across Pin RA11 and Pin RA12, Pin RA21 and Pin RA22, Pin RB11 and Pin RB12, and Pin RB21 and Pin RB22 are not shown in Figure 22, Figure 23, and Figure 24.

Figure 22. ADAQ8088 Direct Coupled to Demodulator, Driving 12-Bit to 14-Bit ADCs with Speeds up to 150 MSPS

Figure 23. Ultrasonic Non-Destructive Test

# **APPLICATIONS INFORMATION**

Figure 24. Multichannel Digitizer Instrument

### **OUTLINE DIMENSIONS**

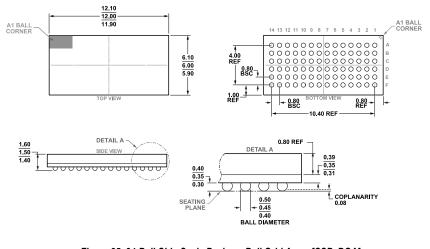

Figure 25. 84-Ball Chip Scale Package Ball Grid Array [CSP\_BGA] (BC-84-4) Dimensions shown in millimeters

Updated: June 14, 2023

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                  | Package Option |

|--------------------|-------------------|--------------------------------------|----------------|

| ADAQ8088BBCZ       | -40°C to +85°C    | 84-Ball CSP-BGA (12mm x 6mm x 1.5mm) | BC-84-4        |

<sup>1</sup> Z = RoHS Compliant Part.

### **EVALUATION BOARDS**

| Model <sup>1</sup> | Package Description |

|--------------------|---------------------|

| EVAL-ADAQ8088EBZ   | Evaluation Board    |

<sup>1</sup> Z = RoHS Compliant Part.