# QUAD SPST JFET ANALOG SWITCH

SW201

## **1.0 SCOPE**

This specification documents the detail requirements for space qualified product manufactured on Analog Devices, Inc.'s QML certified line per MIL-PRF-38535 Level V except as modified herein. The manufacturing flow described in the STANDARD SPACE LEVEL PRODUCTS PROGRAM brochure is to be considered a part of this specification. <a href="http://www.analog.com/aerospace">http://www.analog.com/aerospace</a>. This data sheet specifically details the space grade version of this product. A more detailed operational description and a complete data sheet for commercial product grades can be found at <a href="https://www.analog.com/SW201">www.analog.com/SW201</a>.

**2.0 Part Number**. The complete part number(s) of this specification follow:

Part Number Description

SW201-803Q Quad SPST JFET Analog Switch

## 2.1 Case Outline.

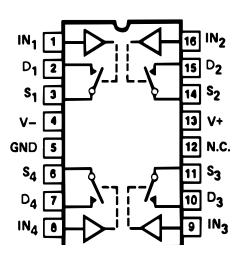

Figure 1 - Terminal connections.

# 2.1.1 SW201 Logic Table:

| Control Logic |              |  |

|---------------|--------------|--|

| Logic Input   | Switch State |  |

| 0             | ON           |  |

| 1             | OFF          |  |

# SW201

| 3.0 | Absolute Maximum Ratings. (T <sub>A</sub> = 25°C, unless or | therwise noted)                         |

|-----|-------------------------------------------------------------|-----------------------------------------|

|     | Operating Temperature Range                                 | 55°C to +125°C                          |

|     | Storage Temperature Range                                   |                                         |

|     | Power Dissipation                                           |                                         |

|     | Lead Temperature (Soldering, 60 sec.)                       |                                         |

|     | Maximum Junction Temperature (T <sub>J</sub> )              |                                         |

|     | V+ Supply to V- Supply                                      |                                         |

|     | V+ Supply to Ground                                         |                                         |

|     | Logic Input Voltage Range                                   | (-4V or V-) to V+ Supply                |

|     | Analog Input Voltage                                        | , , , , , , , , , , , , , , , , , , , , |

|     | Continuous                                                  | V- Supply to V+ Supply +20V             |

|     | 1% Duty Cycle and Driving all 4 inputs                      |                                         |

|     | with 500□S pulse                                            | V- Supply -15V to V+ Supply +20V        |

|     | Maximum Current Through Any Pin                             |                                         |

# 3.1 <u>Thermal Characteristics</u>:

Thermal Resistance, Q (cerdip) Package Junction-to-Case  $(\Theta_{JC})$  = 29°C/W Max Junction-to-Ambient  $(\Theta_{JA})$  = 91°C/W Max

#### **Electrical Table:** 4.0

| TABLE I                                |                        |                                                       |               |              |              |       |

|----------------------------------------|------------------------|-------------------------------------------------------|---------------|--------------|--------------|-------|

| Parameter<br>See notes at end of table | Symbol                 | Conditions<br>VS = ±15V Unless otherwise<br>specified | Sub-<br>group | Limit<br>Min | Limit<br>Max | Units |

| Positive Supply Current                | I+                     | All channels OFF or ON                                | 1             |              | 9            | mA    |

|                                        |                        |                                                       | 2,3           |              | 13.5         |       |

| Negative Supply Current                | l-                     | All Channels OFF or ON                                | 1             |              | 6.0          |       |

|                                        |                        |                                                       | 2,3           |              | 8.5          |       |

| Ground Current                         | IG                     | All Channels OFF or ON                                | 1             |              | 4            |       |

|                                        |                        |                                                       | 2,3           |              | 6            |       |

| Logic "0" Input Current                | I₁∟                    |                                                       | 1             |              | 5            | μА    |

|                                        |                        |                                                       | 2,3           |              | 10           |       |

| Logic "1" Input Current (Note 1)       | Iн                     |                                                       | 1             |              | 5            |       |

|                                        |                        |                                                       | 2,3           |              | 10           |       |

| "ON" Resistance                        | Ron                    | $V_A = -10V$ to 10V; $I_S = 1mA$                      | 1             |              | 80           | Ω     |

|                                        |                        |                                                       | 2,3           |              | 110          |       |

| ΔR <sub>ON</sub> vs. V <sub>A</sub>    | $\Delta R_{\text{ON}}$ | $V_A \leq 10V, I_S = 1mA$                             | 1             |              | 15           | %     |

| Ron Match Between Switches (Note       | Ron                    | $V_A = 0V$ , $I_D = 100 \mu A$                        | 1             |              | 15           |       |

| 3)                                     | (Match)                |                                                       | 2,3           |              | 20           |       |

| Analog Current Range (Note 2)          | IA                     | VS = ±10V                                             | 1             | 10           |              | mA    |

|                                        |                        |                                                       | 2,3           | 7            |              |       |

| Analog Voltage Range (Note 2)          | VA                     | IS = 1mA                                              | 1,2,3         | ±10          |              | V     |

| Source Current "OFF" Condition         | I <sub>S(OFF)</sub>    | VS = +10V, VD = -10V                                  | 1             |              | 2            | nA    |

|                                        |                        |                                                       | 2             |              | 60           |       |

|                                        |                        | VS = -10V, VD = +10V                                  | 1             |              | 2            |       |

|                                        |                        |                                                       | 2             |              | 60           |       |

| Drain Current "OFF" Condition          | ID <sub>(OFF)</sub>    | VS = +10V, VD = -10V                                  | 1             |              | 2            |       |

|                                        |                        |                                                       | 2             |              | 60           |       |

|                                        |                        | VS = -10V, VD = +10V                                  | 1             |              | 2            |       |

|                                        |                        |                                                       | 2             |              | 60           |       |

| Leakage Current "ON" Condition         | I <sub>D(ON)</sub> +   | $VS = VD = \pm 10V$                                   | 1             |              | 2            |       |

|                                        | I <sub>S(ON)</sub>     |                                                       | 2             |              | 100          |       |

| Logic "0" Input Voltage                | V <sub>IL</sub>        |                                                       | 1,2,3         |              | 0.8          | V     |

| Logic "1" Input Voltage                | V <sub>IH</sub>        |                                                       | 1,2,3         | 2            |              | V     |

| Turn-On-Time                           | ton                    | $V_S = -5V$ , $R_L = 1K\Omega$ , $C_L = 13pF$         | 9             |              | 500          | nS    |

| Turn-Off-Time                          | <b>t</b> off           |                                                       | 9             |              | 400          | ]     |

| Break-Before-Make Time                 | ton-toff               |                                                       | 9             | 50           |              |       |

# TABLE I NOTES:

Current Tested at VIN = 2V (worst case condition)  $V_A$ ,  $V_{IH}$ ,  $V_{IL}$  is verified by leakage and  $R_{ON}$  tests.  $R_{ON}$  Match specified as a percentage of  $R_{average}$  where  $R_{average} = RON1 + RON2 + RON3 + RON4$

#### 4.1 **Electrical Test Requirements**:

| Table II                                |                                                         |  |  |  |

|-----------------------------------------|---------------------------------------------------------|--|--|--|

| Test Requirements                       | Subgroups (in accordance with MIL-PRF-38535, Table III) |  |  |  |

| Interim Electrical Parameters           | 1                                                       |  |  |  |

| Final Electrical Parameters             | 1, 2, 3 <u>1/</u> <u>2/</u>                             |  |  |  |

| Group A Test Requirements               | 1, 2, 3, 9                                              |  |  |  |

| Group C end-point electrical parameters | 1 <u>2/</u>                                             |  |  |  |

| Group D end-point electrical parameters | 1                                                       |  |  |  |

| Group E end-point electrical parameters | 1                                                       |  |  |  |

# TABLE II NOTES

- PDA applies to Subgroup 1. Exclude delta's from PDA.

See Table III for delta parameters. See Table I for test conditions.

#### 4.2 Table III. Burn-in test delta limits.

| Table III       |          |       |       |  |

|-----------------|----------|-------|-------|--|

| TEST            | ENDPOINT | DELTA |       |  |

| TITLE           | LIMIT    | LIMIT | UNITS |  |

| R <sub>on</sub> | 80       | ±15   | ohm   |  |

#### 5.0 **Life Test/Burn-In Circuit:**

- HTRB is not applicable for this drawing. 5.1

- Burn-in is per MIL-STD-883 Method 1015 test condition C. 5.2

- 5.3 Steady state life test is per MIL-STD-883 Method 1005.

| Rev | Description of Change                                                                                                                                                                                                                                                                                                      | Date       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Α   | Initiate                                                                                                                                                                                                                                                                                                                   | 7/12/2000  |

| В   | Update web site address. Under max ratings change TJ to TJ. For RON conditions, change $I_D = 1$ mA to $I_S = 1$ mA. RON (Match), change subgroups from 1,2 to 2,3. Break before make specification must a minimum. Add subgroup 9 to Group A requirements on Table II. Change BI circuit from condition A to Condition C. | 12/20/2001 |

| С   | Delete subgroups 4, 5, 6 from Table II, they are not used in Table I. Change paragraph 5.2 from cond. B to Cond. C (BI circuit not changed).                                                                                                                                                                               | 2/21/2002  |

| D   | Update web address. Delete burn-in circuit                                                                                                                                                                                                                                                                                 | 6/20/2003  |

| Е   | Update header/footer & add to 1.0 Scope description.                                                                                                                                                                                                                                                                       | 2/22/2008  |

| F   | Remove obsolete part numbers and update ASD to Analog Devices Standard                                                                                                                                                                                                                                                     | 12/1/2011  |

|     |                                                                                                                                                                                                                                                                                                                            |            |