# 40V Full-Bridge or Dual Half-Bridge Controller

#### **FEATURES**

- Full-Bridge or Dual Half-Bridge Controller

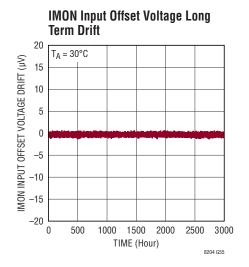

- Dual Bidirectional, Rail-to-Rail Precision Current Monitors (200µV V<sub>OS</sub>)

- Dual On-Chip 16-Bit Monotonic DACs

- 4-Wire SPI with Error Detection and Correction

- Quad N-Channel MOSFET 5.3V Gate Drivers

- V<sub>IN</sub> Range: 5.5V to 40V

- Configurable Output Current or Voltage Regulation

- Configurable PWM Control Methods for Loop Stability

- 100kHz to 1MHz Fixed Switching Frequency with SYNC and Spread Spectrum

- System Monitor and Fault Report via SPI Interface

### **APPLICATIONS**

- Solenoid and Inductive Load Regulation

- Active or Semi-Active Damping Control

- Thermoelectric Cooler (TEC) Control

- Vibration Control

#### DESCRIPTION

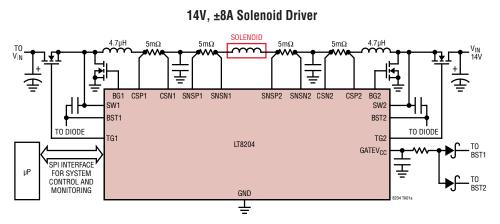

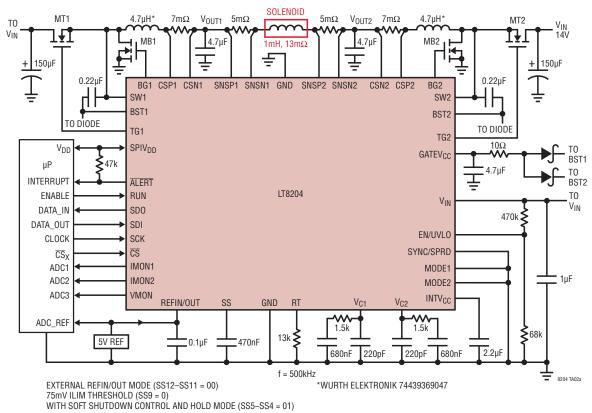

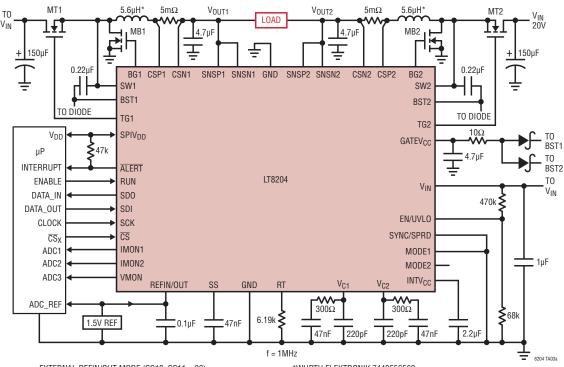

The LT®8204 is a 40V full-bridge or dual half-bridge controller. It can be configured as either a four-switch full-bridge controller or dual two-switch half-bridge controllers to regulate either the output voltage or the output current. The LT8204 provides two selectable PWM control methods (i.e., peak current mode control and voltage mode control) to ease loop frequency compensation for applications with different load types (inductive, resistive, or capacitive loads).

The LT8204 features dual bidirectional rail-to-rail precision ( $200\mu V\ V_{OS}$ ) load current monitors, output voltage monitors, and dual on-chip 16-bit monotonic digital-to-analog converters (DACs). Together with the serial peripheral interface (SPI), the output current or voltage can be programmed precisely on-the-fly. The LT8204 also monitors the system operation status and reports via SPI interface in case of failure (e.g., loss of load connection, failure of external MOSFET devices).

All registered trademarks and trademarks are the property of their respective owners.

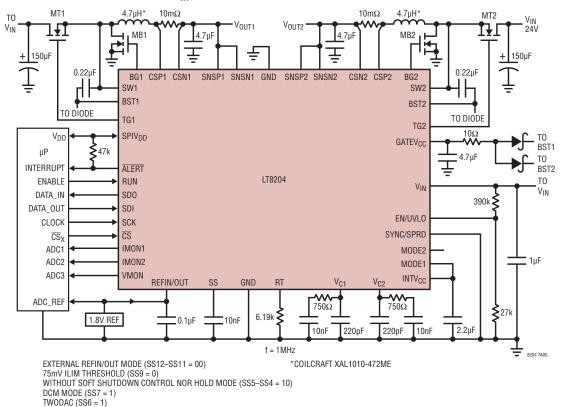

# TYPICAL APPLICATION

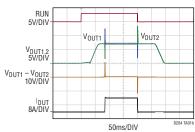

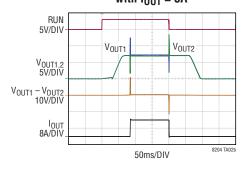

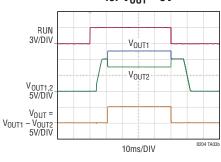

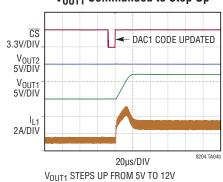

# Soft Start Up and Shutdown with I<sub>OUT</sub> = 8A

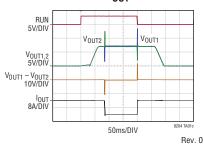

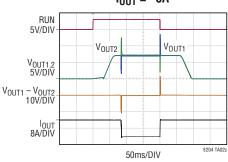

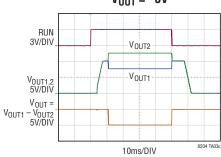

# Soft Start Up and Shutdown with I<sub>OUT</sub> = -8A

- 4

# LT8204

# TABLE OF CONTENTS

| Features                                              | 1            |

|-------------------------------------------------------|--------------|

| Applications                                          | 1            |

| Typical Application                                   | 1            |

| Description                                           |              |

| Absolute Maximum Ratings                              | 3            |

| Order Information                                     | 3            |

| Pin Configuration                                     |              |

| Electrical Characteristics                            |              |

| Typical Performance Characteristics                   |              |

| Pin Functions                                         |              |

| Block Diagram                                         |              |

| Timing Diagram                                        |              |

| Operation                                             |              |

| System Configuration                                  |              |

| Serial Peripheral Interface (SPI)                     |              |

| Internal Registers                                    |              |

| SPI Command Codes                                     |              |

| First SPI Transaction                                 | . 31         |

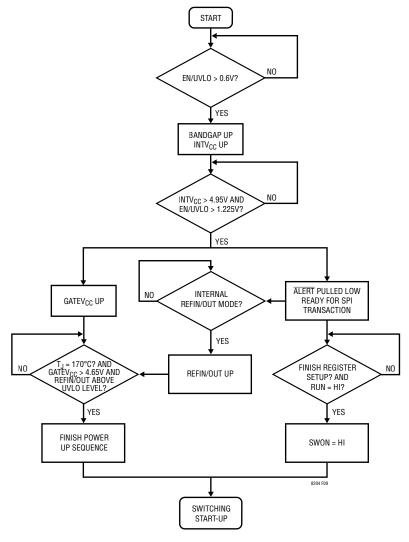

| Power-Up Sequence                                     | . 31         |

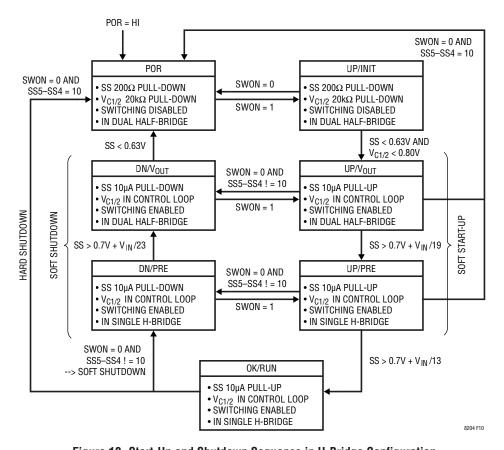

| Start-Up and Shutdown: Full-Bridge                    |              |

| Configuration                                         | .33          |

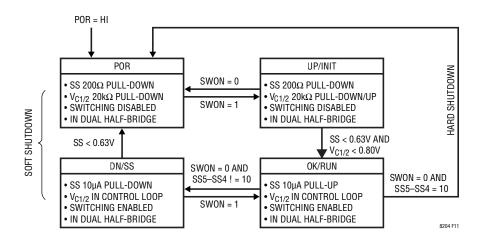

| Start-Up and Shutdown: Dual Half-Bridge               |              |

| Configuration                                         | .34          |

| IMON Output Current Monitoring                        | .35          |

| VMON Differential Output Voltage Monitoring           |              |

| REFIN/OUT Reference Modes                             | .36          |

| Dual 16-Bit DACs                                      |              |

| Fault Detection and Report                            | .36          |

| Applications Information                              |              |

| Shutdown and Programming Undervoltage Lockor          | ut           |

| 39                                                    |              |

| INTV <sub>CC</sub> Regulator Bypassing and Operation  |              |

| GATEV <sub>CC</sub> Regulator Bypassing and Operation |              |

| MODE1 and MODE2 Pin Connection                        |              |

| PWM Control Method Selection                          | -            |

| Switching Frequency Selection                         | .40 <b>R</b> |

| Switching Frequency Setting                                                                          | .40  |

|------------------------------------------------------------------------------------------------------|------|

| Spread Spectrum Frequency Modulation                                                                 |      |

| Frequency Synchronization                                                                            |      |

| Minimum On-Time Considerations                                                                       |      |

| Inductor Current Limit Programming                                                                   | . 41 |

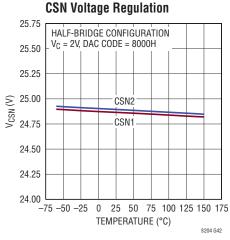

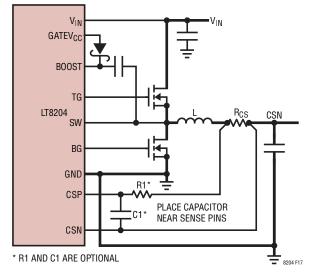

| CSP and CSN Pins                                                                                     | . 41 |

| Low Value Resistors Inductor Current Sensing                                                         | .42  |

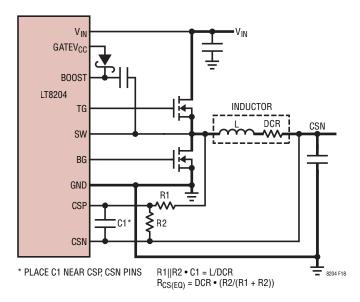

| Inductor DCR Sensing                                                                                 | .42  |

| Slope Compensation and Inductor Peak Current                                                         |      |

| Inductor Selection                                                                                   |      |

| Inductor Core Selection                                                                              | .43  |

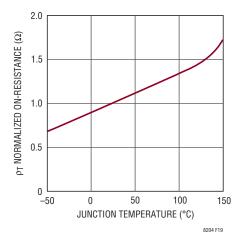

| Power MOSFET Selection                                                                               | .43  |

| Power MOSFET Gate Resistors                                                                          | .44  |

| Optional Schottky Diode (D <sub>T1</sub> , D <sub>B1</sub> , D <sub>T2</sub> , D <sub>B2</sub> )     |      |

| Selection                                                                                            | .45  |

| Top Gate MOSFET Driver Supply (C <sub>BST1</sub> , C <sub>BST2</sub> )                               | .45  |

| Optional Schottky Diode (D <sub>LT1</sub> , D <sub>LB1</sub> , D <sub>LT2</sub> , D <sub>LB2</sub> ) |      |

| Selection                                                                                            |      |

| C <sub>IN</sub> and C <sub>OUT</sub> Selection                                                       | .46  |

| Soft Start-Up and Soft Shutdown                                                                      | .46  |

| Output Current Monitoring and Programming                                                            | . 47 |

| Output Current Sense Resistor R <sub>SNS</sub> Selection                                             | . 47 |

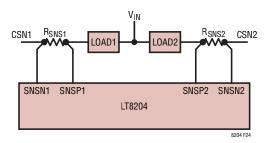

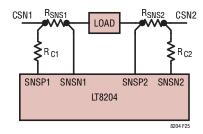

| Output Current Sense Resistor R <sub>SNS</sub> Connection                                            | .48  |

| Output Current Sense Error Sources                                                                   | .48  |

| Output Voltage Monitoring and Programming                                                            |      |

| CSN, CSP, SNSP and SNSN Pins                                                                         | . 50 |

| Loop Compensation                                                                                    | . 50 |

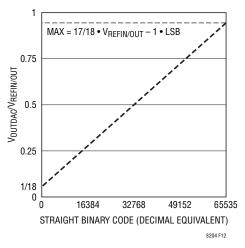

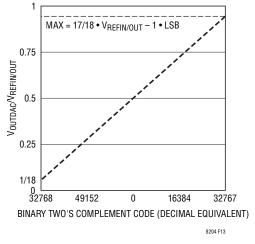

| DAC Output Range                                                                                     | . 51 |

| REFIN/OUT Voltage Reference Considerations                                                           | . 51 |

| ALERT Pin                                                                                            | . 52 |

| Efficiency Considerations                                                                            |      |

| PC Board Layout Checklist                                                                            |      |

| ypical Applications                                                                                  |      |

| ackage Description                                                                                   |      |

| ypical Application                                                                                   |      |

| elated Parts                                                                                         | 58   |

### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| V <sub>IN</sub> , EN/UVLO                                        | 0.3V to 40V    |

|------------------------------------------------------------------|----------------|

| BST1, BST2                                                       | 0.3V to 46V    |

| BST1-SW1, BST2-SW2                                               |                |

| SW1, SW2                                                         |                |

| CSP1, CSN1, CSP2, CSN2                                           |                |

| CSP1-CSN1, CSP2-CSN2                                             |                |

| CSN1-CSN2                                                        |                |

| CSN1-SNSP1, CSN2-SNSP2                                           |                |

| CSN1-SNSN1, CSN2-SNSN2                                           |                |

| SNSP1, SNSN1, SNSP2, SNSN2                                       |                |

| SNSP1-SNSN1, SNSP2-SNSN2                                         |                |

| REFIN/OUT, RUN, SS                                               |                |

| SPIV <sub>DD</sub> , CS, SCK, SDI                                | _0.3V to 6V    |

| SD00.3V to Min (SPI                                              |                |

|                                                                  |                |

| SYNC/SPRD, MODE1, MODE2, ALERT                                   |                |

| GATEV <sub>CC</sub>                                              | 0.37 10 67     |

| INTV <sub>CC</sub> , RT, IMON1, IMON2, VMON, V <sub>C1</sub> , V |                |

| TG1, TG2, BG1, BG2                                               | ` '            |

| Operating Junction Temperature (Notes 3                          | . ,            |

| LT8204R                                                          |                |

| Storage Temperature Range                                        | –65°C to 150°C |

| Lead Temperature (Soldering, 10 sec)                             |                |

| FE Package                                                       | 300°C          |

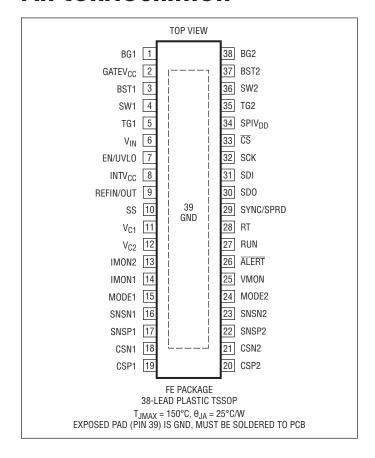

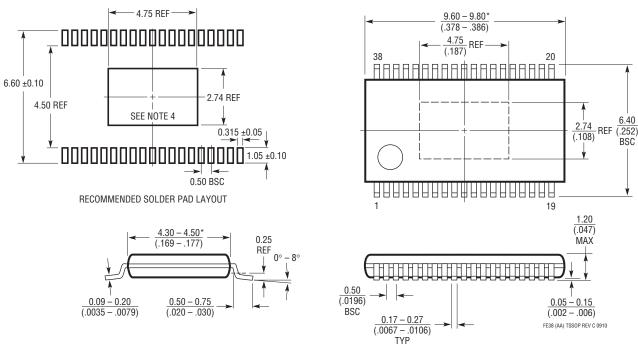

### PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL   | PART MARKING* | PACKAGE DESCRIPTION   | TEMPERATURE RANGE |

|------------------|-----------------|---------------|-----------------------|-------------------|

| LT8204RFE#PBF    | LT8204RFE#TRPBF | LT8204FE      | 38-Lead Plastic TSSOP | -40°C to 150°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

For more information on lead free part marking, go to: http://www.adi.com/leadfree/

For more information on tape and reel specifications, go to: http://www.adi.com/tapeandreel/

| PARAMETER                                         | ARAMETER CONDITIONS                                                                                                    |   |       |                 |                    |                |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---|-------|-----------------|--------------------|----------------|

| Voltage Supplies and Regulators                   | 1                                                                                                                      |   |       |                 |                    |                |

| V <sub>IN</sub> Operating Range                   |                                                                                                                        | • | 5.5   |                 | 40                 | V              |

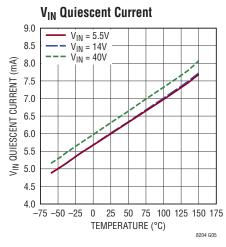

| V <sub>IN</sub> Quiescent Current (Not Switching) | V <sub>RUN</sub> = 0.4V                                                                                                |   |       | 5               | 10                 | mA             |

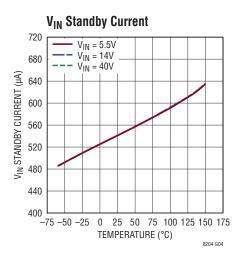

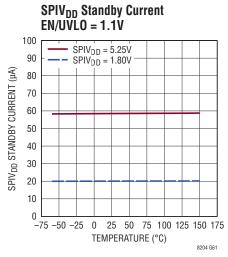

| V <sub>IN</sub> Standby Current                   | V <sub>EN/UVLO</sub> = 1.1V, V <sub>RUN</sub> = 0.4V                                                                   |   |       | 500             |                    | μА             |

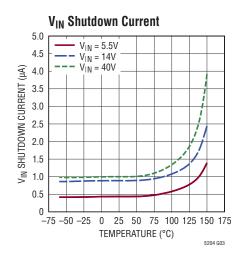

| V <sub>IN</sub> Shutdown Current                  | $V_{EN/UVLO} = 0.3V, V_{RUN} = 0.4V$                                                                                   |   |       | 1               | 2                  | μА             |

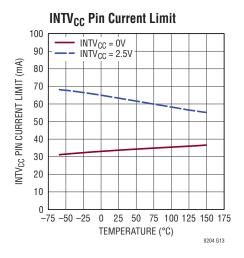

| INTV <sub>CC</sub> Current Limit                  | INTV <sub>CC</sub> = 2.5V                                                                                              |   |       | 60              |                    | mA             |

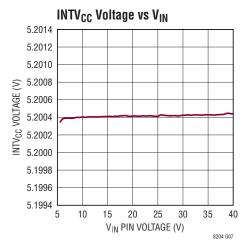

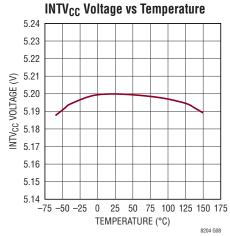

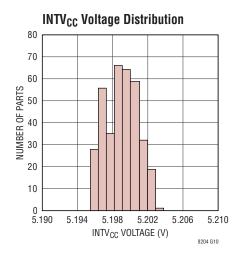

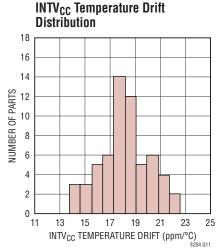

| INTV <sub>CC</sub> Voltage                        | 5.5V ≤ V <sub>IN</sub> ≤ 40V, I <sub>INTVCC</sub> = 10mA                                                               | • | 5.148 | 5.200           | 5.226              | V              |

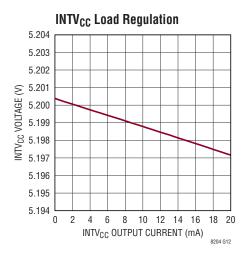

| INTV <sub>CC</sub> Load Regulation                | I <sub>INTVCC</sub> = 0mA to 20mA                                                                                      | • |       |                 | 0.2                | %              |

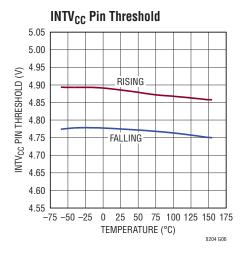

| INTV <sub>CC</sub> Undervoltage Lockout (UVLO)    | INTV <sub>CC</sub> Falling                                                                                             |   | 4.7   | 4.8             | 4.9                | V              |

| INTV <sub>CC</sub> UVLO Hysteresis                |                                                                                                                        |   |       | 120             |                    | mV             |

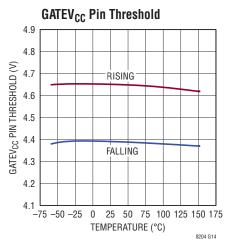

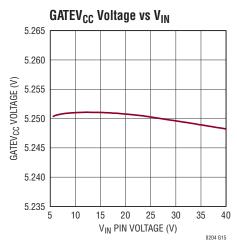

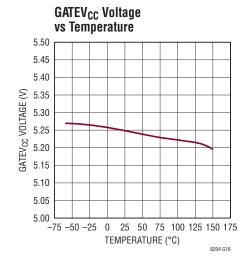

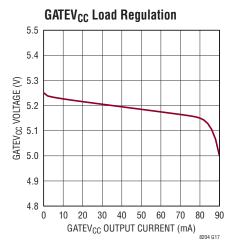

| GATEV <sub>CC</sub> Voltage                       |                                                                                                                        |   | 5.1   | 5.3             | 5.5                | V              |

| GATEV <sub>CC</sub> UVLO                          | GATEV <sub>CC</sub> Falling                                                                                            |   | 4.3   | 4.4             | 4.5                | V              |

| GATEV <sub>CC</sub> UVLO Hysteresis               |                                                                                                                        |   |       | 250             |                    | mV             |

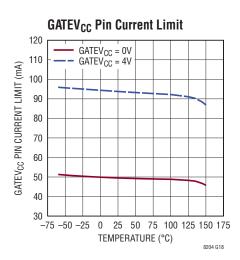

| GATEV <sub>CC</sub> Current Limit                 | GATEV <sub>CC</sub> = 4V                                                                                               |   |       | 100             |                    | mA             |

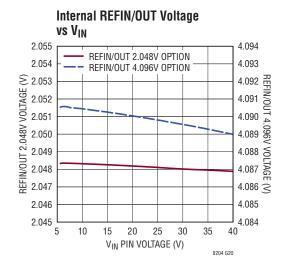

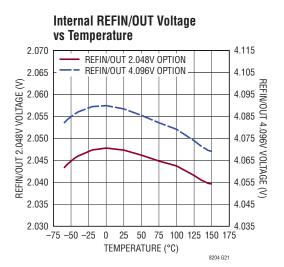

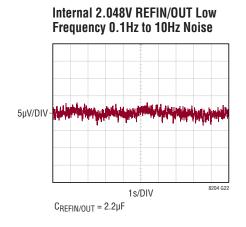

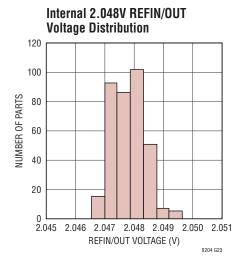

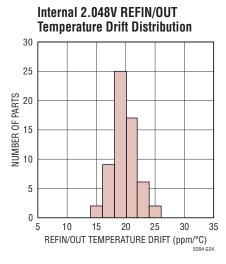

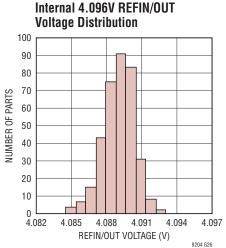

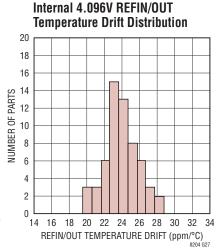

| REFIN/OUT Output Voltage                          | Internal 2.048V REF Mode                                                                                               | • | 2.018 | 2.048           | 2.078              | V              |

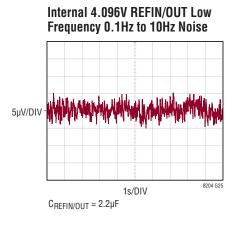

| REFIN/OUT Output Voltage                          | Internal 4.096V REF Mode                                                                                               | • | 4.036 | 4.096           | 4.156              | V              |

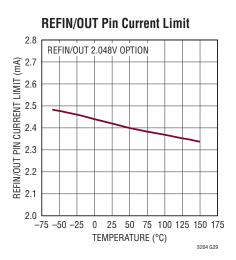

| REFIN/OUT Short-Circuit Current                   | Internal REF Mode, Forcing REFIN/OUT to GND                                                                            |   |       | 2.5             |                    | mA             |

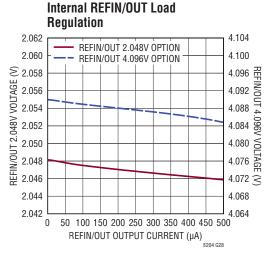

| REFIN/OUT Load Regulation                         | Internal REF Mode, I <sub>OUT</sub> = 500μA                                                                            |   |       | 10              |                    | mV/mA          |

| REFIN/OUT Input Voltage Range                     | External REF Mode                                                                                                      | • | 1.5   |                 | INTV <sub>CC</sub> | V              |

| REFIN/OUT Input Current                           | External REF Mode, V <sub>REFIN/OUT</sub> = 5V                                                                         |   |       | 300             |                    | μА             |

| SPIV <sub>DD</sub> Voltage Range                  |                                                                                                                        | • | 1.80  |                 | 5.25               | V              |

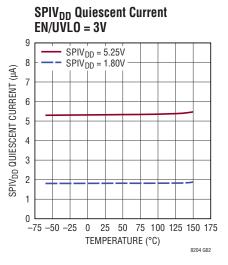

| SPIV <sub>DD</sub> Quiescent Current              | $V_{\overline{CS}} = SPIV_{DD} = 5.25V$                                                                                |   |       | 6               |                    | μА             |

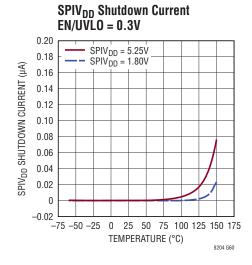

| SPIV <sub>DD</sub> Shutdown Current               | $V_{EN/UVLO} = 0.3V$                                                                                                   |   |       | 0               | 1                  | μA             |

| Switching Regulation Control                      |                                                                                                                        |   |       |                 |                    |                |

| EN/UVLO Shutdown Threshold                        | EN/UVLO Falling, Part Disabled, I <sub>VIN</sub> < 10μA                                                                | • | 0.3   | 0.6             | 1.0                | V              |

| EN/UVLO Threshold                                 | EN/UVLO Falling, Part Stop Switching                                                                                   | • | 1.17  | 1.20            | 1.23               | V              |

| EN/UVLO Hysteresis                                |                                                                                                                        |   |       | 25              |                    | mV             |

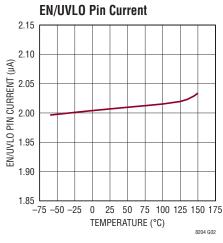

| EN/UVLO Pin Current                               | $V_{EN/UVLO} = 0.3V$<br>$V_{EN/UVLO} = 1.2V$ , EN/UVLO Rising<br>$V_{EN/UVLO} = 1.3V$                                  | • | 1.6   | 0.5<br>2.0<br>0 | 2.6                | μΑ<br>μΑ<br>μΑ |

| RUN High Level Input Voltage                      |                                                                                                                        | • | 1.30  |                 | ,                  | V              |

| RUN Low Level Input Voltage                       |                                                                                                                        | • |       |                 | 0.55               | V              |

| RUN Resistance to GND                             |                                                                                                                        |   | ,     | 100             |                    | kΩ             |

| SS Hard Pull-Down Resistance                      | V <sub>RUN</sub> = 0.4V                                                                                                |   |       | 250             |                    | Ω              |

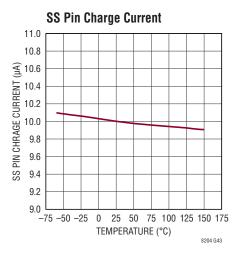

| SS Charging Current                               | V <sub>SS</sub> = 1.5V                                                                                                 |   | 9     | 10              | 11                 | μA             |

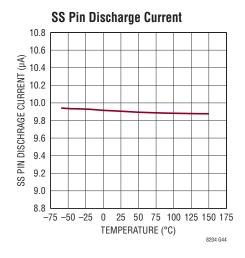

| SS Discharging Current                            | V <sub>SS</sub> = 1.5V, V <sub>RUN</sub> = 0.4V                                                                        |   | 9     | 10              | 11                 | μА             |

| CSPx, CSNx Common Mode Operating Voltage Range    |                                                                                                                        | • | 0     |                 | 40                 | V              |

| CSNx + CSPx + SNSPx + SNSNx Pin Current           | $V_{EN/UVL0} = 0.3V$ , $V_{RUN} = 0.4V$ , $0V < V_{CSPx} = V_{CSNx} = V_{SNSPx} = V_{SNSNx} < 40V$                     | • |       | 0.5             | 2                  | μА             |

| CSNx Pin Current                                  | $ \begin{vmatrix} V_{CSPX} = V_{CSNX} = 7V, V_{RUN} = 0.4V \\ V_{CSPX} = V_{CSNX} = 0V, V_{RUN} = 0.4V \end{vmatrix} $ |   |       | 300<br>-10      |                    | μA<br>μA       |

| PARAMETER                                                                                             | CONDITIONS                                                                                                                                            |   | MIN                          | TYP                   | MAX                      | UNITS          |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------------|-----------------------|--------------------------|----------------|

| CSPx Pin Current                                                                                      | $V_{CSPx} = V_{CSNx} = 7V$ , $V_{RUN} = 0.4V$<br>$V_{CSPx} = V_{CSNx} = 0V$ , $V_{RUN} = 0.4V$                                                        | • | −1.5<br>−1.5                 | -1.0<br>-1.0          | 0                        | μA<br>μA       |

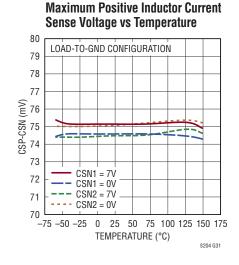

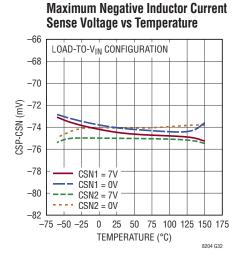

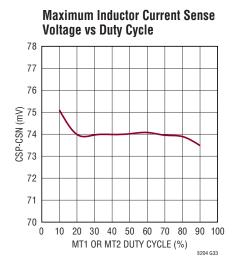

| Maximum Current Sense Threshold (V <sub>CSPx</sub> – V <sub>CSNx</sub> )                              | Full-Bridge Configuration<br>Positive<br>Negative                                                                                                     |   | 55<br>-95                    | 75<br>-75             | 95<br>-55                | mV<br>mV       |

|                                                                                                       | Dual Half-Bridge Configuration, Load-To-GND Positive                                                                                                  |   | 55                           | 75                    | 95                       | mV             |

|                                                                                                       | Dual Half-Bridge Configuration, Load-To-V <sub>IN</sub><br>Negative                                                                                   |   | -95                          | -75                   | -55                      | mV             |

| Error Amp g <sub>m</sub>                                                                              | $V_{VC1} = V_{VC2} = 2V$                                                                                                                              |   |                              | 1.2                   |                          | mS             |

| Maximum V <sub>C1</sub> and V <sub>C2</sub> Pin Current                                               | Source<br>Sink                                                                                                                                        |   |                              | –180<br>180           |                          | μA<br>μA       |

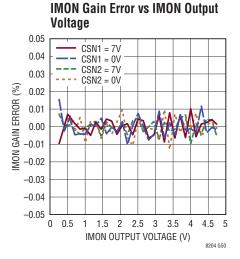

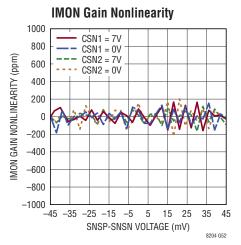

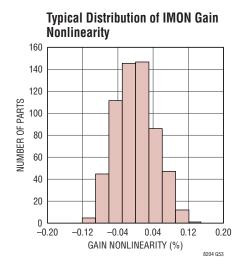

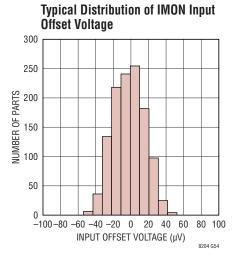

| Output Current Monitor                                                                                |                                                                                                                                                       |   |                              |                       |                          |                |

| SNSPx, SNSNx Common Mode Operating Voltage Range                                                      |                                                                                                                                                       | • | 0                            |                       | 40                       | V              |

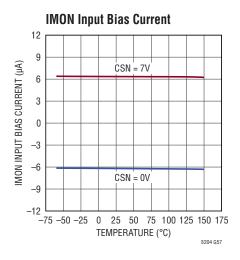

| SNSPx, SNSNx Pin Bias Current $I_{Bx}$ I(SNSPx) = I(SNSNx) (Note 4)                                   | V <sub>SNSPx</sub> = V <sub>SNSNx</sub> = 7V<br>V <sub>SNSPx</sub> = V <sub>SNSNx</sub> = 0V                                                          | • | 4.2<br>-8.4                  | 6.3<br>-6.3           | 8.4<br>-4.2              | μA<br>μA       |

| SNSPx, SNSNx Pin Offset Current I <sub>OSx</sub> ,<br>I <sub>OSx</sub> = I(SNSPx) – I(SNSNx) (Note 4) | V <sub>SNSPx</sub> = V <sub>SNSNx</sub> = 7V<br>V <sub>SNSPx</sub> = V <sub>SNSNx</sub> = 0V                                                          | • | -1<br>-1                     |                       | 1                        | μA<br>μA       |

| SNSPx, SNSNx Differential Operating Voltage Range                                                     |                                                                                                                                                       | • | -45                          |                       | 45                       | mV             |

| V <sub>SNSPx</sub> – V <sub>SNSNx</sub> to IMONx Voltage Gain                                         | V <sub>SNSPx</sub> = 0V, V <sub>SNSPx</sub> - V <sub>SNSNx</sub> = ±45mV<br>V <sub>SNSPx</sub> = 40V, V <sub>SNSPx</sub> - V <sub>SNSNx</sub> = ±45mV | • | 49.8<br>49.8                 | 50<br>50              | 50.2<br>50.2             | mV/mV<br>mV/mV |

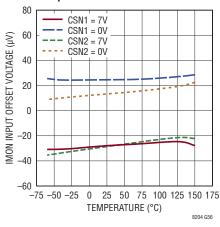

| V <sub>SNSPx</sub> – V <sub>SNSNx</sub> Input Referred Offset Voltage for IMONx                       | $V_{SNSPx} = V_{SNSNx} = 0V$<br>$V_{SNSPx} = V_{SNSNx} = 40V$                                                                                         | • | -120<br>-200<br>-150<br>-200 | 0<br>0<br>0<br>0      | 120<br>200<br>150<br>200 | μV<br>μV<br>μV |

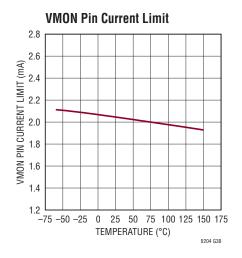

| IMONx Short-Circuit Current                                                                           | IMONx = 0V                                                                                                                                            |   |                              | 2                     |                          | mA             |

| IMONx Overcurrent Threshold                                                                           |                                                                                                                                                       |   |                              | 1.8                   |                          | mA             |

| IMONx Undervoltage Threshold                                                                          | IMONx Falling, External REFIN/OUT Mode  VREFIN/OUT = 5V  VREFIN/OUT = 3V  VREFIN/OUT = 1.5V                                                           |   |                              | 135<br>75<br>30       |                          | mV<br>mV<br>mV |

| IMONx Undervoltage Hysteresis                                                                         |                                                                                                                                                       |   |                              | 15                    |                          | mV             |

| IMONx Overvoltage Threshold                                                                           | IMONx Rising, External REFIN/OUT Mode  VREFIN/OUT = 5V  VREFIN/OUT = 3V  VREFIN/OUT = 1.5V                                                            |   |                              | 4.85<br>2.91<br>1.455 |                          | V<br>V<br>V    |

| IMONx Overvoltage Hysteresis                                                                          |                                                                                                                                                       |   |                              | 15                    |                          | mV             |

| Output Current Regulation Loop                                                                        |                                                                                                                                                       |   |                              |                       |                          |                |

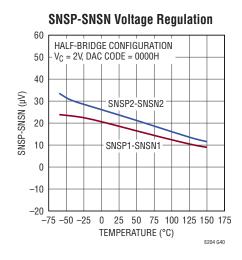

| V <sub>SNSPx</sub> – V <sub>SNSNx</sub> Regulation Voltage for Output<br>Current Control              | DAC Code = 7FFFH, V <sub>SNSPx</sub> = 0V, 7V<br>DAC Code = 0000H, V <sub>SNSPx</sub> = 0V, 7V<br>DAC Code = 8000H, V <sub>SNSPx</sub> = 0V, 7V       | • | 44.00<br>-0.25<br>-44.88     | 44.44<br>0<br>-44.44  | 44.88<br>0.25<br>-44.00  | mV<br>mV<br>mV |

| Output Voltage Monitor and Differential Regulation                                                    | Loop                                                                                                                                                  |   |                              |                       |                          |                |

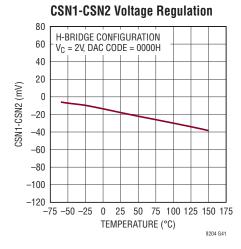

| V <sub>CSN1</sub> - V <sub>CSN2</sub> Operating Voltage Range                                         |                                                                                                                                                       | • | -40                          |                       | 40                       | V              |

| V <sub>CSN1</sub> - V <sub>CSN2</sub> to VMON Voltage Gain                                            | V <sub>CSN1</sub> - V <sub>CSN2</sub> = 40V                                                                                                           | • | 49                           | 50                    | 51                       | mV/V           |

| VMON Short-Circuit Current                                                                            | VMON = 0V                                                                                                                                             |   |                              | 2                     |                          | mA             |

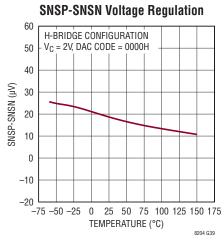

| V <sub>CSN1</sub> – V <sub>CSN2</sub> Regulation Voltage                                              | DAC Code = 0000H                                                                                                                                      |   |                              | 0                     |                          | V              |

| PARAMETER                                             | CONDITIONS                                                  |   | MIN                         | TYP                                 | MAX                         | UNITS       |

|-------------------------------------------------------|-------------------------------------------------------------|---|-----------------------------|-------------------------------------|-----------------------------|-------------|

| External NMOS Gate Drive                              |                                                             |   |                             |                                     |                             |             |

| TG1, TG2 Rise Time                                    | C <sub>LOAD</sub> = 3300pF (Note 5)                         |   |                             | 20                                  |                             | ns          |

| TG1, TG2 Fall Time                                    | C <sub>LOAD</sub> = 3300pF (Note 5)                         |   |                             | 20                                  |                             | ns          |

| BG1, BG2 Rise Time                                    | C <sub>LOAD</sub> = 3300pF (Note 5)                         |   |                             | 20                                  |                             | ns          |

| BG1, BG2 Fall Time                                    | C <sub>LOAD</sub> = 3300pF (Note 5)                         |   |                             | 20                                  |                             | ns          |

| TG1 Off to BG1 On Delay                               | $C_{LOAD}(TG1) = C_{LOAD}(BG1) = 3300pF \text{ (Note 5)}$   |   |                             | 50                                  |                             | ns          |

| BG1 Off to TG1 On Delay                               | $C_{LOAD}(BG1) = C_{LOAD}(TG1) = 3300pF $ (Note 5)          |   |                             | 30                                  |                             | ns          |

| TG2 Off to BG2 On Delay                               | $C_{LOAD}(TG2) = C_{LOAD}(BG2) = 3300pF \text{ (Note 5)}$   |   |                             | 50                                  |                             | ns          |

| BG2 Off to TG2 On Delay                               | $C_{LOAD}(BG2) = C_{LOAD}(TG2) = 3300pF $ (Note 5)          |   |                             | 30                                  |                             | ns          |

| Minimum On-Time for TG1, BG2                          | $C_{LOAD}(TG1) = C_{LOAD}(BG2) = 3300pF$                    |   |                             | 150                                 |                             | ns          |

| Minimum Off-Time for TG1, BG2                         | $C_{LOAD}(TG1) = C_{LOAD}(BG2) = 3300pF$                    |   |                             | 150                                 |                             | ns          |

| MT1, MT2, MB1 and MB2 V <sub>DS</sub> Fault Threshold | Positive<br>Negative                                        |   |                             | 1.5<br>-1.0                         |                             | V           |

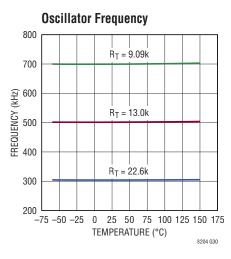

| Oscillator                                            |                                                             |   |                             |                                     |                             |             |

| Switch Frequency Range                                | SYNCing or Free Running                                     |   | 100                         |                                     | 1000                        | kHz         |

| Switching Frequency                                   | RT = 90.9k                                                  |   | 90                          | 100                                 | 110                         | kHz         |

|                                                       | RT = 22.6k<br>RT = 13.0k                                    |   | 280<br>475                  | 300<br>500                          | 320<br>525                  | kHz<br>kHz  |

| SYNC/SPRD High Level Input Voltage                    | 111 10.0K                                                   | • | 1.30                        |                                     | 020                         | V           |

| SYNC/SPRD Low Level Input Voltage                     |                                                             | • | 1.00                        |                                     | 0.55                        | V           |

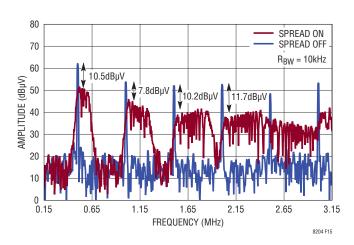

| Spread Spectrum Above Oscillator Frequency            | V <sub>SYNC/SPRD</sub> = 3V                                 |   |                             | 23                                  | 0.00                        | —— <u> </u> |

| Switching Phase Between Two Half Bridges              | In Dual Half-Bridge Mode, RT = 13.0k                        |   | 160                         | 180                                 | 200                         | Deg         |

| Digital to Analog Conversion                          |                                                             |   |                             |                                     |                             |             |

| Resolution                                            | (Note 6)                                                    | • | 16                          |                                     |                             | Bits        |

| Monotonicity                                          |                                                             | • | 16                          |                                     |                             | Bits        |

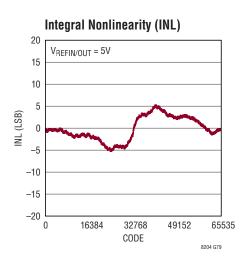

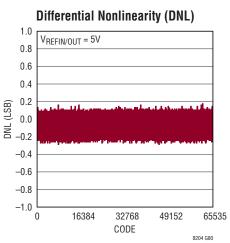

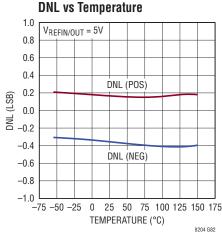

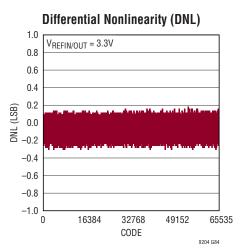

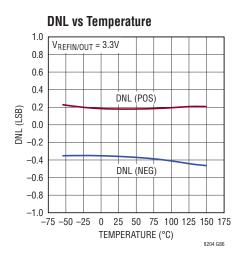

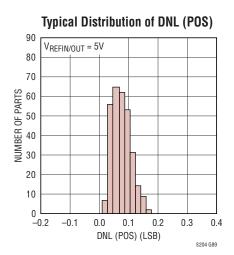

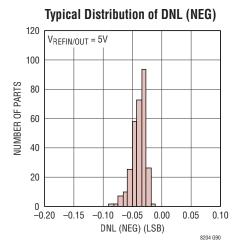

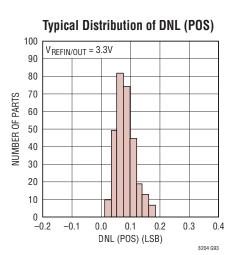

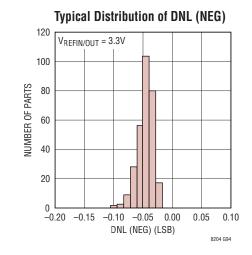

| Differential Nonlinearity (DNL)                       |                                                             | • |                             | ±0.5                                | ±1                          | LSB         |

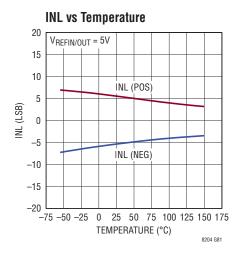

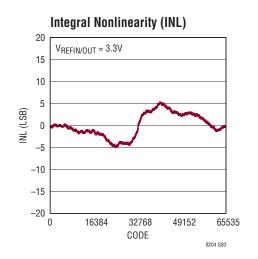

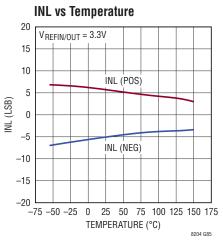

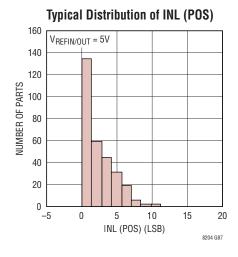

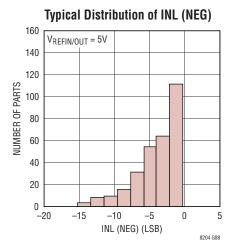

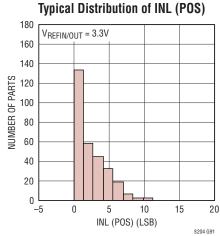

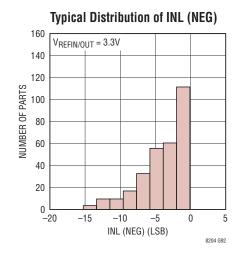

| Integral Nonlinearity (INL)                           |                                                             | • |                             | ±20                                 | ±40                         | LSB         |

| DAC Min Output Voltage                                |                                                             |   |                             | 1/18 • V <sub>REFIN/OUT</sub>       |                             | V           |

| DAC Max Output Voltage                                | (Note 7)                                                    | Н |                             | 17/18 •                             |                             | V           |

| Drie max output voltage                               | (Note 1)                                                    |   |                             | V <sub>REFIN/OUT</sub> − 1<br>• LSB |                             | ٧           |

| Logic I/O                                             |                                                             |   |                             |                                     |                             |             |

| ALERT Output Low Voltage                              | I <sub>ALERT</sub> = 1mA                                    | • |                             |                                     | 0.3                         | V           |

| ALERT Output High to Low Delay Time                   |                                                             |   |                             | 1                                   |                             | μs          |

| ALERT Leakage Current                                 | V <sub>ALERT</sub> = 5.25V                                  | • |                             |                                     | 2                           | μА          |

| CS, SCK, SDI High Level Input Voltage                 |                                                             | • | 0.8 •<br>SPIV <sub>DD</sub> |                                     |                             | V           |

| CS, SCK, SDI Low Level Input Voltage                  |                                                             | • |                             |                                     | 0.2 •<br>SPIV <sub>DD</sub> | V           |

| CS, SCK, SDI Input Leakage                            | $V_{\overline{CS}} = V_{SCK} = V_{SDI} = SPIV_{DD} = 5.25V$ | • |                             |                                     | ±2                          | μА          |

| CS, SCK, SDI Input Capacitance                        | (Note 6)                                                    |   |                             | 10                                  |                             | pF          |

| PAR             | AMETER                                                                         | CONDITIONS                                                                                        | MIN | TYP                         | MAX | UNITS    |            |

|-----------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|-----------------------------|-----|----------|------------|

| SD0             | High Level Output Voltage                                                      | I <sub>SD0</sub> = -500μA                                                                         | •   | SPIV <sub>DD</sub><br>- 0.2 |     |          | V          |

| SD0             | Low Level Output Voltage                                                       | I <sub>SDO</sub> = 500μA                                                                          | •   |                             |     | 0.2      | V          |

| SD0             | Hi-Z Output Leakage Current                                                    | $V_{SDO} = 0V \text{ to } SPIV_{DD}$                                                              | •   |                             |     | ±1       | μА         |

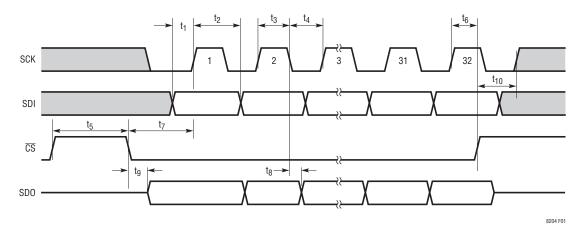

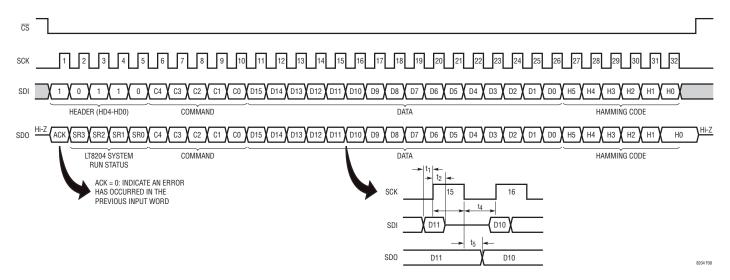

| SPI             | Timing (See SPI Timing Diagram in Figure 1) (l                                 | Note 5)                                                                                           | ·   |                             |     |          |            |

| $\bar{t}_1^-$   | SDI Valid to SCK Setup                                                         |                                                                                                   | •   | 5                           |     |          | ns         |

| t <sub>2</sub>  | SDI Valid to SCK Hold                                                          |                                                                                                   | •   | 5                           |     |          | ns         |

| t <sub>3</sub>  | SCK Pulse Width High                                                           |                                                                                                   | •   | 15                          |     |          | ns         |

| t <sub>4</sub>  | SCK Pulse Width Low                                                            |                                                                                                   | •   | 15                          |     |          | ns         |

| t <sub>5</sub>  | CS Pulse Width High                                                            |                                                                                                   | •   | 25                          |     |          | ns         |

| $t_6$           | Last Bit SCK High to CS High                                                   |                                                                                                   | •   | 10                          |     |          | ns         |

| t <sub>7</sub>  | CS Low to SCK High                                                             |                                                                                                   | •   | 10                          |     |          | ns         |

| t <sub>8</sub>  | SDO Data Valid Delay from SCK Low                                              | C <sub>L</sub> = 20pF<br>SPIV <sub>DD</sub> = 3.3V to 5.25V<br>SPIV <sub>DD</sub> = 1.80V to 3.3V | •   |                             |     | 20<br>45 | ns<br>ns   |

| t <sub>9</sub>  | SDO Data Valid Delay from CS Low                                               | C <sub>L</sub> = 20pF<br>SPIV <sub>DD</sub> = 3.3V to 5.25V<br>SPIV <sub>DD</sub> = 1.80V to 3.3V | •   |                             |     | 20<br>45 | ns<br>ns   |

| t <sub>10</sub> | CS High to SCK High                                                            |                                                                                                   | •   | 10                          |     |          | ns         |

|                 | SCK Frequency (Note 8)                                                         | 50% Duty Cycle<br>SPIV <sub>DD</sub> = 3.3V to 5.25V<br>SPIV <sub>DD</sub> = 1.80V to 3.3V        | •   |                             |     | 25<br>10 | MHz<br>MHz |

|                 | EN/UVLO High to Part Responsive to $\overline{\text{CS}}$ Low (Power-Up Delay) | C <sub>INTVCC</sub> = 2.2μF                                                                       |     |                             | 500 |          | μs         |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Do not apply a voltage or current source to these pins. They must be connected to resistive/capacitive loads only, otherwise permanent damage may occur.

**Note 3:** The LT8204 includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 150°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

LT8204R is specified over the -40°C to 150°C operating junction temperature range. High junction temperatures degrade operating lifetimes. Operating lifetime is derated at junction temperature greater than 125°C. Note the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance, and other environmental factors.

**Note 4:**  $I_{B1(2)}$  is defined as the average of the input bias currents to the SNSP1(2) and SNSN1(2) pins. A positive current indicates current flowing into the pin.  $I_{OS1(2)}$  is defined as the difference of the input bias currents.  $I_{OS1(2)} = I_{SNSP1(2)} - I_{SNSN1(2)}$ .

Note 5: Rise and fall times are measured using 10% and 90% levels. Delay times are measured using 50% levels.

Note 6: Guaranteed by design and not production tested.

**Note 7:** LSB voltage value is defined as 8/9 • V<sub>REFIN/OUT</sub>/2<sup>16</sup>.

Note 8: When using SDO, the maximum SCK frequency  $f_{\text{MAX}}$  is limited by SDO propagation delay as following:

$$f_{MAX} = \frac{1}{2 \cdot (t_8 + t_S)}$$

where  $t_8$  is SDO data valid delay time from  $\overline{\text{CS}}$  low, and  $t_S$  is the setup time of the receiving device.

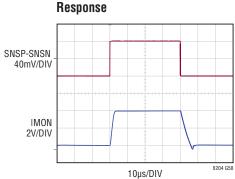

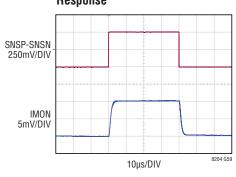

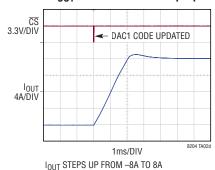

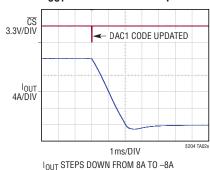

**IMON Large-Signal Step**

#### **IMON Small-Signal Step** Response

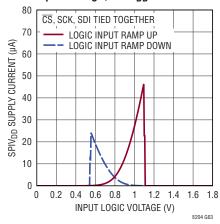

SPIV<sub>DD</sub> Supply Current vs Logic Input Voltage, SPIV<sub>DD</sub> = 1.8V

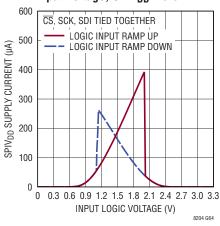

SPIV<sub>DD</sub> Supply Current vs Logic Input Voltage, SPIV<sub>DD</sub> = 3.3V

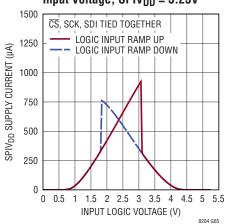

$SPIV_{DD}$  Supply Current vs Logic Input Voltage,  $SPIV_{DD} = 5.25V$

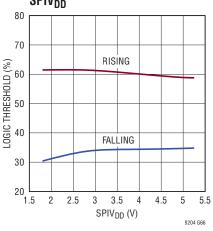

CS, SCK, SDI Logic Threshold vs SPIVDD

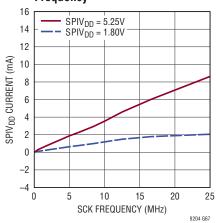

SPIV<sub>DD</sub> Supply Current of Update Frequency

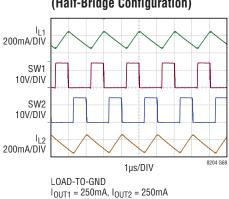

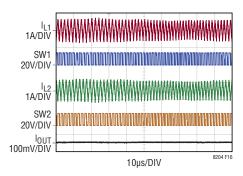

**Switching Waveforms** (Half-Bridge Configuration)

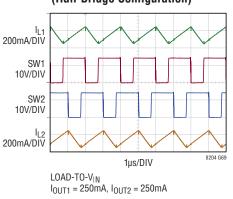

**Switching Waveforms** (Half-Bridge Configuration)

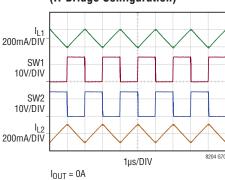

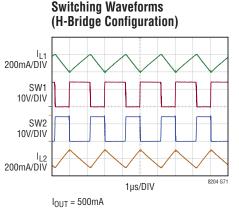

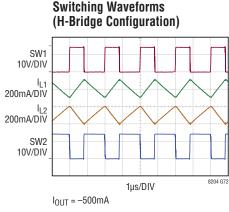

**Switching Waveforms** (H-Bridge Configuration)

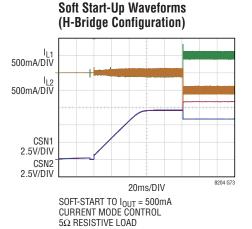

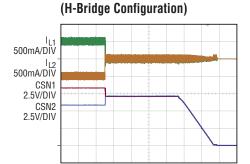

Soft Startdown Waveforms

SOFT SHUTDOWN FROM  $I_{OUT} = 500 \text{mA}$  CURRENT MODE CONTROL  $5\Omega$  RESISTIVE LOAD

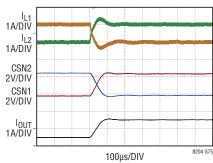

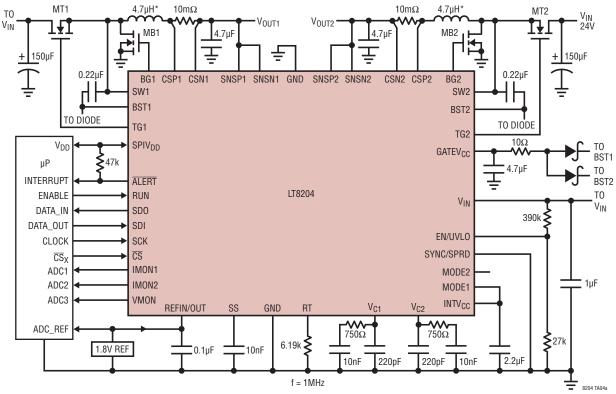

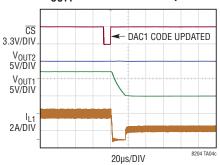

#### I<sub>OUT</sub> Step Response to DAC (H-Bridge Configuration)

I<sub>OUT</sub> TRANSITION FROM -500mA TO 500mA CURRENT MODE CONTROL  $5\Omega$  RESISTIVE LOAD

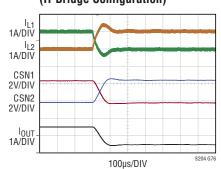

#### I<sub>OUT</sub> Step Response to DAC (H-Bridge Configuration)

I<sub>OUT</sub> TRANSITION FROM 500mA TO -500mA CURRENT MODE CONTROL  $5\Omega$  RESISTIVE LOAD

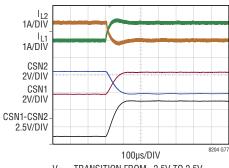

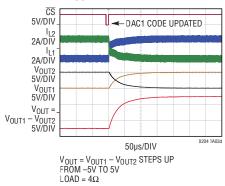

#### **VOUT Step Response to DAC** (H-Bridge Configuration)

V<sub>OUT</sub> TRANSITION FROM –2.5V TO 2.5V CURRENT MODE CONTROL  $5\Omega$  RESISTIVE LOAD

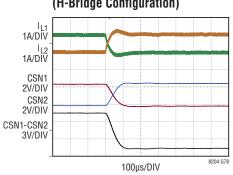

#### Vout Step Response to DAC (H-Bridge Configuration)

V<sub>OUT</sub> TRANSITION FROM 2.5V TO –2.5V CURRENT MODE CONTROL  $5\Omega$  RESISTIVE LOAD

### PIN FUNCTIONS

**BG1**, **BG2** (**Pins 1, 38**): Bottom N-Channel MOSFET Gate Driver Output Pin. BG1 and BG2 are the gate drive signals for the external N-channel MOSFET devices connected between the SW1 and SW2 pins and power ground. The BG1 and BG2 voltage swings between GATEV<sub>CC</sub> and ground.

**GATEV<sub>CC</sub>** (**Pin 2**): Internal 5.3V Regulator Bypass Pin. The internal bottom gate drivers are powered from this voltage. Decouple this pin to power ground with at least 4.7µF low ESR ceramic capacitor placed close to the IC.

**BST1**, **BST2** (**Pins 3**, **37**): Boosted Floating Gate Driver Supply Pin. The positive (+) terminals of the bootstrap capacitors connect to these pins. The BST1 and BST2 pin voltages swing from a diode voltage below GATEV<sub>CC</sub> to ( $V_{IN}$  + GATEV<sub>CC</sub>).

**SW1**, **SW2** (**Pins 4**, **36**): Switch Pins. The negative (–) terminals of the bootstrap capacitors connect to these pins.

**TG1**, **TG2** (**Pins 5**, **35**): Top N-Channel MOSFET Gate Driver Output Pin. TG1 and TG2 are the gate drive signals for the external N-channel MOSFET connected between  $V_{IN}$  and the SW1 and SW2 pins. The voltage swing on the TG1 and TG2 pins equals GATEV<sub>CC</sub> superimposed onto the SW1 and SW2 pin voltages.

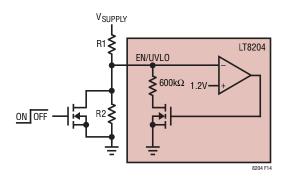

$V_{IN}$  (Pin 6): Input Supply Pin. Must be locally bypassed with a capacitor to ground.

**EN/UVLO (Pin 7):** Enable and Undervoltage Lockout Pin. Pull the pin below 0.3V to shut down the LT8204 for lowest  $V_{IN}$  current. This pin has an accurate 1.2V (typical) falling threshold and programs  $V_{IN}$  undervoltage lockout (UVLO) threshold with an external resistor divider from  $V_{IN}$  to ground. A 2 $\mu$ A pin current hysteresis programs  $V_{IN}$  UVLO hysteresis. If neither function is used, tie this pin directly to  $V_{IN}$ .

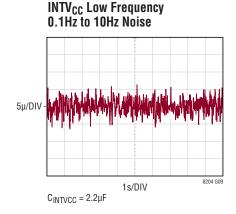

INTV<sub>CC</sub> (Pin 8): Internal 5.2V Regulator Bypass Pin. The internal control circuits are powered from this voltage. Decouple this pin to signal ground with at least  $2.2\mu F$  low ESR ceramic capacitor placed close to the IC. The 5.2V output voltage on this pin features high accuracy over a wide range of  $V_{IN}$  voltage, load current and temperature, and thus can be used as  $V_{REFIN/OUT}$  (tied to the REFIN/OUT pin), if no external precise voltage reference is available.

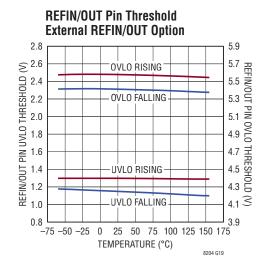

**REFIN/OUT (Pin 9):** Reference Input/Output Pin. This pin provides the voltage reference for the on-chip DACs and the precision current monitors. It acts as the internal reference output in internal reference mode and acts as the reference input pin in external reference mode. In internal reference mode, two voltage options (2.048V or 4.096V) can be selected via the SPI interface. Decouple this pin to signal ground with a low ESR ceramic capacitor placed close to the IC, for best noise performance.

**SS** (Pin 10): Soft Start-Up/Soft Shutdown Pin. Connect a capacitor between the SS pin and ground for soft start-up and soft shutdown controls. See more details in the Applications Information section.

$V_{C1}$ ,  $V_{C2}$  (Pins 11, 12): Error Amplifier Output Pins. Connect the external closed-loop frequency compensation network to these pins.

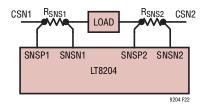

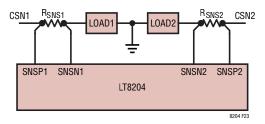

**IMON1, IMON2 (Pins 14, 13):** Load Current Monitor 1 and 2 Output Pin. The voltage on IMON1(2) pin is 50 times the voltage  $(V_{SNSP1(2)} - V_{SNSN1(2)})$ , plus an offset of  $V_{REFIN/OUT}/2$ . A pin voltage above  $V_{REFIN/OUT}/2$  indicates a current flow from SNSP1 pin to SNSN1 pin, while a voltage below  $V_{REFIN/OUT}/2$  for the opposite current flow direction.

**MODE1**, **MODE2** (Pins 15, 24): Mode Pins. The voltage applied to these pins sets the system architecture of the LT8204. See more details in Table 1.

**SNSN1, SNSN2 (Pins 16, 23):** Load Current Monitor Negative (–) Input Pins.

**SNSP1, SNSP2 (Pins 17, 22):** Load Current Monitor Positive (+) Input Pins. These two pins and the SNSN1, SNSN2 pins measure the voltage across the sense resistors, to monitor the load current.

**CSN1**, **CSN2** (**Pins 18**, **21**): Inductor Current Sense Negative (–) Input Pins. See more details in the Applications Information section.

**CSP1**, **CSP2** (**Pins 19**, **20**): Inductor Current Sense Positive (+) Input Pins. The  $V_C$  pin voltage and built-in offsets between CSP1(2) and CSN1(2), in conjunction with the current sense resistor value, set the current trip threshold. Short these pins to  $V_{CSN1}$  and  $V_{CSN2}$  respectively if not used. See more details in the Applications Information section.

### PIN FUNCTIONS

**VMON (Pin 25):** Differential Load Voltage Monitor Output Pin. The pin voltage is 1/20 of the differential voltage  $(V_{CSN1} - V_{CSN2})$  plus an offset of  $V_{REFIN/OUT}/2$ . A pin voltage above  $V_{REFIN/OUT}/2$  indicates a higher voltage on the CSN1 pin than the CSN2 pin, while a voltage below  $V_{REFIN/OUT}/2$  for the opposite voltage direction.

**ALERT (Pin 26):** Alert Pin. Connect a pull-up resistor from this pin to SPIV<sub>DD</sub> or an external voltage source. Limit the current into the pin to no more than 1mA. This pin is active low when the LT8204 has an alert. Connect this pin to a microprocessor's interrupt pin for system diagnosis.

**RUN (Pin 27):** System Run Pin. This pin is used to disable/enable the switching action of the LT8204. Pull this pin low to disable the switching action. If a soft shutdown command is programmed through the SPI interface (by default, the LT8204 commands a soft shutdown), the LT8204 performs the soft shutdown to discharge the output voltages of the bridge/s to near zero voltage, before stopping switching; If a hold command is programmed through the SPI interface, the LT8204 first performs the soft shutdown and then turns on both bottom MOSFETs. (See more details in the Operation section). If the function is not used, tie this pin directly to INTV<sub>CC</sub>.

RT (Pin 28): Timing Resistor Input Pin. The RT pin adjusts the LT8204 switching frequency. Place a resistor from this pin to the ground to set the free-running frequency. If floated or disconnected from the resistor at any time, LT8204 will default to a 30kHz switching frequency and notify the host of this abnormal frequency in a fault status register. Similarly, if the RT pin is shorted to ground, it will default to a 1.4MHz switching frequency and notify the host.

**SYNC/SPRD (Pin 29):** External Synchronization Input or Spread Spectrum Control Pin. To synchronize the switching frequency to an external clock, simply drive this pin with a clock. Connect this pin to  $INTV_{CC}$  to use the internal oscillator frequency with a +23% triangle spread spectrum. If spread spectrum is not needed, tie this pin to the ground to use the fixed internal oscillator frequency.

**SDO** (**Pin 30**): Tri-State Serial Data Output Pin. The SDO pin is the SPI digital communication port from the LT8204 to the host microprocessor. During the data output period, this pin is used as serial data output. When the  $\overline{CS}$  pin is HIGH, the SDO pin is in a high impedance state. This allows sharing of the serial interface with other devices.

**SDI (Pin 31):** Serial Data Input Pin. The SDI pin is the SPI digital communication port from the host microprocessor to the LT8204. SDI sends the 32-bit command instruction to the LT8204 at the rising edge of SCK. The input word is encoded with Hamming code to allow for error detection and correction by the LT8204. The LT8204 accepts input word lengths of 32 bits. See Figure 8.

**SCK (Pin 32):** Serial Clock Input Pin. The SCK pin is the clock input for the SPI digital communication between the host and the LT8204. The SCK pin is used to synchronize the data transfer. Each bit of data is shifted into the SDI pin on the rising edge of the serial clock, while each bit of data is shifted out of the SDO pin on the falling edge of the serial clock.

$\overline{\text{CS}}$  (Pin 33): SPI Chip Select Pin. The  $\overline{\text{CS}}$  pin is the chip select input for the SPI digital communication between the host microprocessor and the LT8204. When  $\overline{\text{CS}}$  is active low, SCK is enabled, and the selected LT8204 is allowed to receive and transmit data across a shared SPI communication bus. When  $\overline{\text{CS}}$  is high, SCK is disabled, and the specified command (See Figure 1) is executed.

**SPIV**<sub>DD</sub> (**Pin 34**): External SPI Interface Supply Voltage Pin. Connect this pin to the same voltage potential as the host microprocessor to make sure the output voltage level of the SDO pin is compatible with the host microprocessor. Decouple this pin to ground with a low ESR ceramic capacitor placed close to the IC.

**GND (Exposed Pad Pin 39):** Ground Pin. The exposed pad of the TSSOP package is an electrical connection to GND. To ensure proper electrical and thermal performance, tie the exposed pad directly to the local ground plane.

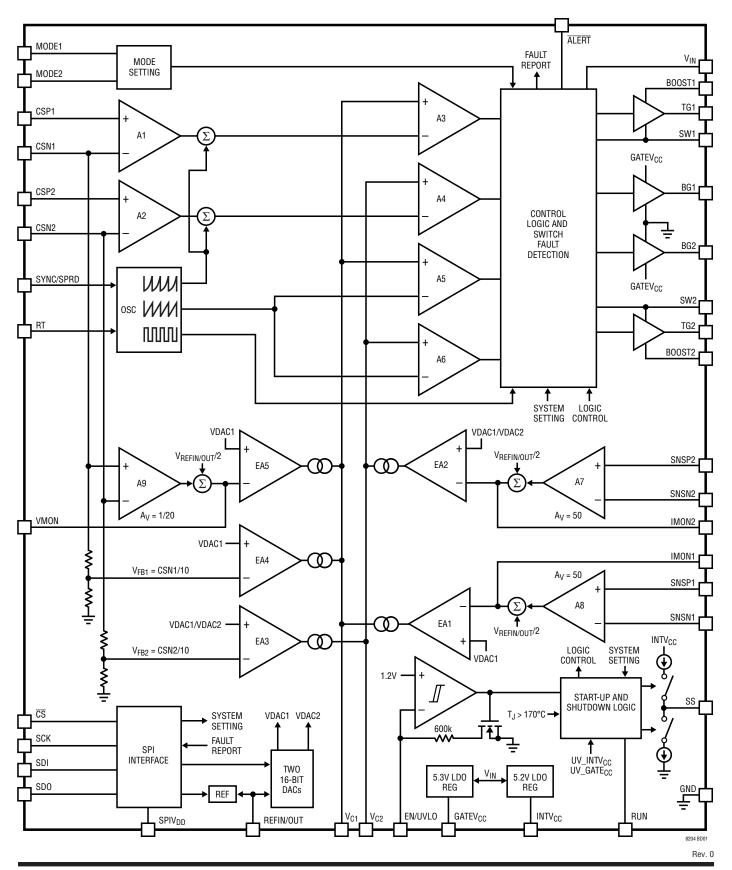

# **BLOCK DIAGRAM**

# TIMING DIAGRAM

Figure 1. SPI Timing Diagram

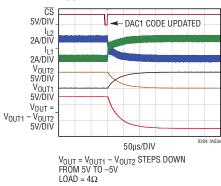

The LT8204 integrates quad N-channel MOSFET gate drivers. It can be configured as either a four-switch full-bridge controller or a dual two-switch half-bridge controller. In terms of output regulation, it can be either the output current regulation or the output voltage regulation. The LT8204 provides two selectable PWM control methods, i.e., voltage mode control or peak current mode control, to ease loop compensation for applications with different load types. Operation is best understood by referring to the typical application circuit on the front page and the Block Diagram.

#### SYSTEM CONFIGURATION

The LT8204 configures the system architecture based on the MODE1 and MODE2 pin connections, as shown in Table 1. Note that configurations #1 and #9 are the same.

#### **Topology**

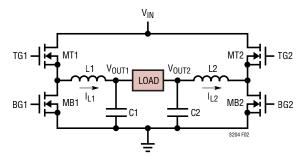

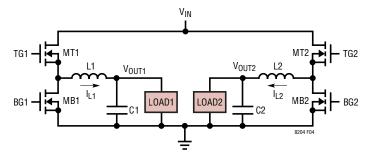

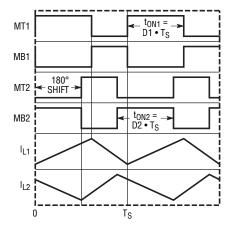

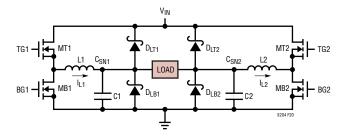

The LT8204 can be configured as a four-switch full-bridge controller, as shown in Figure 2, with the power switches controlled as shown in Figure 3. At the beginning of every cycle, switches MT1 and MB2 are turned on, and both the L1 and L2 inductor current ramps up. When switches MT1 and MB2 are commanded to be turned off by the control loop, switches MB1 and MT2 are turned on for the rest of the cycle, and both L1 and L2 inductor current ramps down.  $V_{OUT1}$  and  $V_{OUT2}$  voltages are regulated at D •  $V_{IN}$  and (1-D) •  $V_{IN}$ , respectively, and therefore the voltage across the load is  $V_{OUT1}$  –  $V_{OUT2}$  = (2D-1) •  $V_{IN}$ .

Figure 2. Simplified Diagram of the Four-Switch Full-Bridge

Figure 3. Operation of the Four-Switch H-Bridge

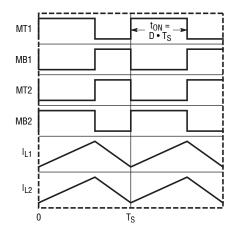

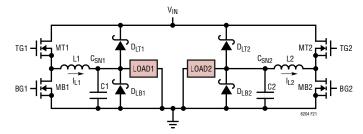

The LT8204 can also be configured as a dual two-switch half-bridge controller, as shown in Figure 4, with the power switches controlled as shown in Figure 5. The two half bridges operate 180° out of phase with each other to minimize the power loss and noise. At the beginning of every clock cycle, switch MT1 is turned on, and L1

| Table 1. System Configuration Based on MODE1 and MODE2 Pin Connection (0 = Low (Tie to | o GND). Z = Floa | t. 1 = High (lie to INIVcc)) |

|----------------------------------------------------------------------------------------|------------------|------------------------------|

|----------------------------------------------------------------------------------------|------------------|------------------------------|

|     |       |       |                 |                  | SYSTEM CONFIG  | GURATION       |              |              |

|-----|-------|-------|-----------------|------------------|----------------|----------------|--------------|--------------|

| No. | MODE2 | MODE1 | TOP             | OLOGY            | OUTPUT RE      | GULATION       | PWM CONTI    | ROL METHOD   |

|     |       |       | SINGLE H-BRIDGE | DUAL HALF-BRIDGE | OUTPUT CURRENT | OUTPUT VOLTAGE | VOLTAGE MODE | CURRENT MODE |

| 1   | 0     | 0     | X               |                  | Х              |                | Х            |              |

| 2   | 0     | 1     | Х               |                  | Х              |                |              | Х            |

| 3   | 1     | 0     |                 | Х                | Х              |                | Х            |              |

| 4   | 1     | 1     |                 | X                | Х              |                |              | Х            |

| 5   | 0     | Z     | Х               |                  |                | Х              | Х            |              |

| 6   | Z     | 0     | X               |                  |                | X              |              | Х            |

| 7   | 1     | Z     |                 | X                |                | X              | X            |              |

| 8   | Z     | 1     |                 | Х                |                | X              |              | Х            |

| 9   | Z     | Z     | X               |                  | X              |                | X            |              |

Figure 4. Simplified Diagram of the Dual Two-Switch Half-Bridge

Figure 5. Operation of the Dual Two-Switch Half-Bridge

inductor current ramps up. When switch MT1 is commanded to be turned off by the control loop, switch MB1 is turned on for the rest of the cycle, and L1 inductor current ramps down. The turn-on of the switch MT2 in the second half-bridge is 180° out of phase to the clock. There is a second separate control loop to command the switch MT2 to turn off and then turn on switch MB2.  $V_{OUT1}$  and  $V_{OUT2}$  voltages are regulated at D1  $\bullet$   $V_{IN}$  and D2  $\bullet$   $V_{IN}$ , respectively.

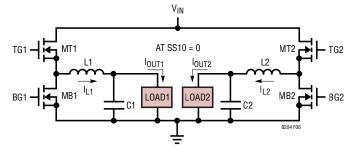

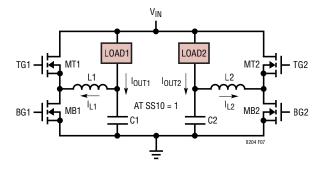

### **Output Regulation**

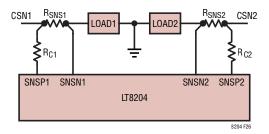

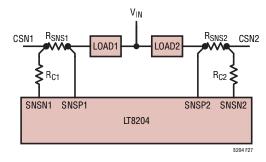

The LT8204 regulates either the output voltage or the output current. For the full-bridge configuration, the output regulation can be bidirectional, either the output voltage or the output current. For the dual half-bridge configuration, the output voltage regulation can only be a positive value reference to GND, while the output current regulation can be either direction depending on the state of bit SS10 in the system setup register (see Internal Registers section). In Figure 6, at SS10 = 0, the

output current flows out of the LC filter, and the half-bridge operates as a current source for a load reference to GND (Load-to-GND). In Figure 7, at SS10 = 1, the output current flows into the LC filter, and the half-bridge operates as a current sink for a load reference to  $V_{IN}$  (Load-to- $V_{IN}$ ).

#### **PWM Control Method**

The LT8204 features two PWM control methods: voltage mode control and peak current mode control.

In the voltage mode control, the  $V_{C}$  pin voltage compares with an internal voltage ramp (see the PWM comparators A5 and A6 in the block diagram) and hence determines the duty cycle of the SW pin switching waveform.

In the peak current mode control, the  $V_{C}$  pin voltage determines the peak current in the inductor (see the inductor current sense amplifiers A1 and A2 and the PWM comparators A3 and A4 in the block diagram) and hence the duty cycle of the SW pin switching waveform.

Figure 6. Dual Half-Bridge as Current Sources with Load-to-GND

Figure 7. Dual Half-Bridge as Current Sources with Load-to-VIN

#### SERIAL PERIPHERAL INTERFACE (SPI)

The LT8204 uses SPIV<sub>DD</sub>,  $\overline{\text{CS}}$ , SCK, SDI, and SDO pins for SPI communication. When the  $\overline{\text{CS}}$  pin is taken low, the data on the SDI pin is loaded into the shift register on the rising edge of the clock (SCK pin). The 5-bit header, HD4 to HD0 = 10110, is loaded first, followed by the 5-bit command word, C4 to C0, and then the 16-bit data word, D15 to D0, and finally the 6-bit hamming code, H5 to H0, in straight binary format. Data can only be transferred to the LT8204 when the  $\overline{\text{CS}}$  signal is low. The rising edge of  $\overline{\text{CS}}$  ends the data transfer and causes the device to carry out the action specified in the 32-bit input word.

The LT8204 also shifts out data on the SDO pin when the  $\overline{\text{CS}}$  pin is low. At the falling edge of  $\overline{\text{CS}}$ , a 1-bit acknowledgement ACK, is presented on the SDO pin, and then on the falling edges of the clock (SCK pin), the 4-bit system run status word, SR3 to SR0, is shifted out, followed by the 5-bit command, C4 to C0, and then the 16-bit data word, D15 to D0, and finally the 6-bit hamming code, H5 to H0, in straight binary format. Data can only be transferred from the LT8204 when the  $\overline{\text{CS}}$  signal is low. The rising edge of  $\overline{\text{CS}}$  ends the data transfer and causes the SDO pin to be in high impedance mode.

The complete sequence for SPI data transfer to and from the LT8204 is shown in Figure 8.

#### **Null SPI Transaction**

The LT8204 allows a null SPI transaction, in which the  $\overline{CS}$  pin can be pulsed low without a clock on the SCK pin. With this feature, the host microprocessor ( $\mu P$ ) can check if the previous transaction was acknowledged by the first data bit shown on the SDO pin, i.e., the ACK bit, after the  $\overline{CS}$  pin is low. The  $\mu P$  can then make a decision on the next SDI input word while the  $\overline{CS}$  pin is pulled high without clocking the SCK pin. After the null SPI transaction, the ACK bit is set to 1.

#### **Error Detection and Correction**

During the SPI transaction, both the 32-bit input word for the SDI data and the 32-bit output word for the SDO data incorporate a 6-bit hamming code for error detection and correction.

Table 2 shows the parity bit coverage map provided by the 6-bit hamming code, and Table 3 shows the equations to generate the 6-bit hamming code (with an example provided). With 6 parity bits for 26 data bits, the hamming code used in the LT8204 features the capability of single-error correction and double-error detection.

#### **SPI Transaction Acknowledgement**

The ACK bit is set to 1 when the previous SPI transaction was accepted by the LT8204. It is set to 0 when any of the following conditions happen: number of SCK clock not equal to 0 or 32 within a  $\overline{\text{CS}}$  pin low pulse; double errors detected in the transaction; misuse of command codes (see SPI Command Codes section). In addition to set the ACK bit to 0 in case of a fault in the transaction, the  $\overline{\text{ALERT}}$  pin is also pulled low until the next  $\overline{\text{CS}}$  pin falling edge.

#### System Run Status Word, SR3 to SR0

The 4-bit system run status word, SR3 to SR0, reports the system run status of the LT8204 right before the falling edge of the  $\overline{CS}$  pin, shown in Table 4. Note that only the seven codes shown in Table 4 are valid for system run status. If any one of the other codes not listed in Table 4 is received by the  $\mu R$  it indicates either a SPI transaction error

Figure 8. SPI 32-Bit Load Sequence

Table 2. Parity Bit Coverage Map by the Hamming Code (Note: the data on the 1st SCK period is defined as B25, followed by B24 on the 2nd SCK period, and finally B0 on the 26th SCK period.)

| 26-Bit<br>Data Bit    |       |    |    | B25 |    | B24 | B23 | B22 |    | B21 | B20 | B19 | B18 | B17 | B16 | B15 |    | B14 | B13 | B12 | B11 | B10 | В9 | B8 | В7 | B6 | B5 | В4 | ВЗ | B2 | B1 | ВО |    |

|-----------------------|-------|----|----|-----|----|-----|-----|-----|----|-----|-----|-----|-----|-----|-----|-----|----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|----|

| Correspor<br>SDI Data | nding | НО | Н1 | HD4 | Н2 | HD3 | HD2 | HD1 | Н3 | HD0 | C4  | C3  | C2  | C1  | CO  | D15 | Н4 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Н5 |

| Correspor<br>SDO Data |       | НО | H1 | ACK | H2 | S3  | S2  | S1  | НЗ | S0  | C4  | C3  | C2  | C1  | C0  | D15 | H4 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Н5 |

| Parity Bit            | Н0    | Х  |    | Х   |    | х   |     | Х   |    | х   |     | Х   |     | Х   |     | Х   |    | Х   |     | Х   |     | Х   |    | Х  |    | Х  |    | Х  |    | Χ  |    | Х  |    |

| Coverage              | H1    |    | Х  | Х   |    |     | Х   | Х   |    |     | Х   | Х   |     |     | Х   | Х   |    |     | Х   | Х   |     |     | Х  | Х  |    |    | Х  | Х  |    |    | Х  | Х  | Г  |

|                       | H2    |    |    |     | Х  | Х   | Х   | Х   |    |     |     |     | Х   | Х   | Х   | Х   |    |     |     |     | Х   | Х   | Х  | Х  |    |    |    |    | Х  | Х  | Х  | Х  |    |

|                       | Н3    |    |    |     |    |     |     |     | Х  | Х   | Х   | Х   | Х   | Х   | Х   | Х   |    |     |     |     |     |     |    |    | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |    |

|                       | H4    |    |    |     |    |     |     |     |    |     |     |     |     |     |     |     | Х  | Х   | Х   | Х   | Х   | Х   | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |    |

|                       | Н5    | Х  | Х  | Х   | Х  | х   | Х   | Х   | Х  | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х  | Х   | Х   | Х   | Х   | Х   | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

**Table 3. Hamming Code Generation**

| PARITY BIT | BIT GENERATION                                                                      |

|------------|-------------------------------------------------------------------------------------|

| HO         | XOR (B25, B23, B21, B19, B17, B15, B13, B11–B10, B8, B6, B4–B3, B1–B0)              |

| H1         | XOR (B25-B24, B21-B20, B17-B16, B13-B12, B10-B9, B6-B5, B3, B2, B0)                 |

| H2         | XOR (B25 to B22, B17 to B14, B10 to B7, B3 to B1)                                   |

| Н3         | XOR (B25 to B18, B10 to B4)                                                         |

| H4         | XOR (B25 to B11)                                                                    |

| H5         | XOR (B25 to B0, H4 to H0)                                                           |

|            | <b>Example:</b> For B25 to B0 = 1011 0001 0110 1010 1010 1010 10, H5 to H0 = 001101 |

Table 4. System Run Status Word

| SR3 TO SR0 | SYSTEM RUN STATUS                                                                                                                           |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 0000       | Switching stopped; waiting for the $\mu P$ to set up the system setup register                                                              |

| 0001       | Switching stopped; waiting for GATEV $_{\rm CC}$ , REFIN/OUT, V $_{\rm C}$ or SS pin voltage to be ready, or thermal shutdown to be cleared |

| 0010       | Switching stopped; waiting for RUN pin to go high                                                                                           |

| 0011       | In Hold Mode; waiting for RUN pin to go high                                                                                                |

| 0100       | In soft shutdown                                                                                                                            |

| 0101       | In soft start-Up                                                                                                                            |

| 0111       | Running                                                                                                                                     |

| 1100       | Running at IMON1 with PMOS input pair and IMON2 with PMOS input pair                                                                        |

| 1101       | Running at IMON1 with NMOS input pair and IMON2 with PMOS input pair                                                                        |

| 1110       | Running at IMON1 with PMOS input pair and IMON2 with NMOS input pair                                                                        |

| 1111       | Running at IMON1 with NMOS input pair and IMON2 with NMOS input pair                                                                        |

due to  $\overline{CS}$  pin connection or sequence error (if SR3 to SR0 = 0110) or a system setup issue (if SR3 to SR0 = 10xx).

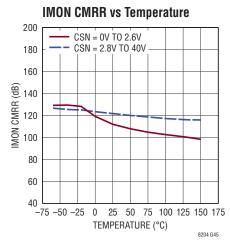

The last four codes, SR3–SR0 = 11xx, shown in the table indicate the operation modes of the dual IMON current monitors during system running. To achieve rail-to-rail operation, the LT8204 IMON design detects the input common mode and selects different input pairs accordingly. When the current sense pins, SNSP and SNSN pins, have a common mode voltage of higher than 2.7V (typical), the IMON current monitor selects the NMOS input pair;

when the common mode voltage is lower than 2.3V (typical), the IMON current monitor selects the PMOS input pair.

#### **INTERNAL REGISTERS**

The LT8204 has six internal registers: system setup register, DAC1 register, DAC2 register, AlertMask register, bit flip register and fault status register. These registers are initialized to all 0 when the EN/UVLO pin voltage is lower than its rising threshold.

#### **System Setup Register**

The system setup register maintains the commands to set up the LT8204 system operation, as shown in Table 5.

**SS15 to SS13:** These three bits, HBRIDGE, VMODE, and IFB, indicate the system configuration as shown in Table 1, and they are read only through the SPI transaction. The  $\mu P$  can utilize these bits to confirm the system configuration before starting switching.

**SS12, SS11:** The SS12 bit, REF\_INT, selects internal REFIN/OUT mode at 1 and external REFIN/OUT mode at 0. In the internal REFIN/OUT mode with SS12 = 1, the SS11 bit, REF\_INT\_LOW, further defines the voltage value at the REFIN/OUT pin: 2.048V at 1 and 4.096V at 0. For the  $\mu$ P to write into SS12–SS11 bits, the LT8204 should be in non-switching mode, i.e., when the SR3, SR2 bits in the system run status word are not 11 and the RUN pin is low.

**SS10**: The SS10 bit, LOAD\_TO\_VIN, is used only in the dual half-bridge configuration with output current

**Table 5. System Setup Register**

| SS15                                           | SS14                                                                            | SS13                                                                                  | SS12                                                                      | SS11                                                                  | SS10                                                        | <b>SS9</b>                                               | 888                                                              |  |

|------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------|--|

| HBRIDGE<br>1: in H-Bridge<br>0: in Half-Bridge | VMODE<br>1: in Voltage<br>Mode Control<br>0: in Peak<br>Current Mode<br>Control | IFB<br>1: in Output<br>Current<br>Regulation<br>0: in Output<br>Voltage<br>Regulation | REF_INT<br>1: Internal<br>REFIN/OUT Mode<br>0: External<br>REFIN/OUT Mode | REF_INT_LOW 1: 2.048V Internal REFIN/OUT 0: 4.096V Internal REFIN/OUT | LOAD_TO_VIN<br>1: Load-to-V <sub>IN</sub><br>0: Load-to-GND | LOW_ILIM<br>1: 25mV<br>Threshold<br>0: 75mV<br>Threshold | IN_PHASE<br>1: in Phase<br>Control<br>0: out of Phase<br>Control |  |

| \$\$7                                          | <b>SS6</b>                                                                      | \$\$5                                                                                 | \$\$4                                                                     | <b>SS3</b>                                                            | SS2                                                         | SS1                                                      | SSO                                                              |  |

| DCM<br>1: in DCM Mode<br>0: in CCM Mode        | OCM Mode 1: use DAC2 1: without for the Second Shute                            |                                                                                       | HOLD<br>1: with Hold<br>Mode<br>0: without Hold<br>Mode                   | Must be 0                                                             | Must be 0                                                   | SETUP_DONE1<br>11: setup Done<br>10: setup Not<br>Done   | SETUP_DONEO<br>01: setup Not<br>Done<br>00: setup Not<br>Done    |  |