# 0.38 GHz to 12 GHz RxVGA

### **FEATURES**

- ▶ Broadband RxVGA interfacing LNA and beamformer to RF ADC

- Operating frequency range: 0.38 GHz to 12 GHz, 2 product variants

- ▶ ADL6332-A: 0.38 GHz to 8 GHz

- ▶ ADL6332-B: 1.0 GHz to 12 GHz

- Differential signal chain optimizes common-mode rejection of RF ADC, even order harmonics and intermodulation

- $\blacktriangleright$  50 Ω single-ended input and 50 Ω differential output

- ▶ Integrated broadband RF input balun

- ▶ 70 dB of gain control range in 1 dB step

- ▶ RF DSA range: 24.0 dB with 1.0 dB step

- ▶ Amplifier bypass loss of 12 dB each

- ► Asynchronous toggle between multiple pre-defined attenuation values and bypass amplifier stages

- Power gain at 4 GHz: 15.3 dB (ADL6332-A), 15.4 dB (ADL6332-B)

- Noise figure at 4 GHz: 8.6 dB (ADL6332-A), 8.3 dB (ADL6332-B)

- ▶ OIP3 at 4 GHz: 31.3 dBm (ADL6332-A), 32.5 dBm (ADL6332-B)

- ▶ OIP2 at 4 GHz: 57 dBm (ADL6332-A), 62 dBm (ADL6332-B)

- OP1dB at 4 GHz: 12.7 dBm (ADL6332-A), 13.0 dBm (ADL6332-B)

- ▶ Fully programmable through a 3-/4-wire SPI

- ▶ Single 3.3 V supply

- ▶ 24-terminal, 4.0 mm x 4.0 mm LGA

### **APPLICATIONS**

- ▶ Aerospace and defense

- Instrumentation and test equipment

- ▶ Communication system

## **GENERAL DESCRIPTION**

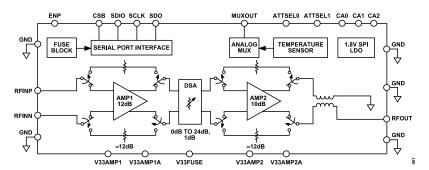

The ADL6332 RxVGA is intended to provide an interface from LNA/Beam Former/Rx Front End to RF Analog to Digital Converters (RF-ADC). Each ADL6332 IC is composed of a balun, two differential RF amplifiers with bypass attenuators, and a digital step attenuator (DSA) to provide suitable receiver performance in a 24-terminal, 4.0 mm x 4.0 mm LGA package.

Serial-port interface (SPI) control is available to configure RF signal path or to optimize supply current vs. performance.

An integrated RF balun is used to provide a single-ended output over 0.38 GHz to 8.0 GHz (ADL6332-A) or 1.0 GHz to 12.0 GHz (ADL6332-B) with good impedance match.

Table 1. ADL6332 Frequency Ranges

| ADL6332 Variant | Frequency Range (GHz) |

|-----------------|-----------------------|

| A               | 0.38 to 8.0           |

| В               | 1.0 to 12.0           |

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

# **NOTES**