# EDN 电子技术设计

EDN-China

## 技术论坛

# 高速信号发生应用中的关键要求

作者: Clarence Mayott, 凌力尔特公司混合信号产品部应用工程师

在高速信号发生应用中, 带宽和分辨率是关键要求。新型信号发生应用运用高速数模转换器(DAC)来产生各种不同类型的波形, 包括单音直至具数百兆赫兹带宽、复杂的多通道波形。这些应用要求高速DAC足够快, 以在不牺牲模拟性能的前提下产生这些波形。在很多信号发生应用中, 相位噪声会限制通道的数量以及可能实现的通道间隔。传统上, 相位噪声由驱动DAC时钟输入的时钟信号引起, 不过DAC增加的任何相位噪声都会出现在输出频谱中, 并限制可能产生的信号。对任何通用信号发生应用而言, 理想DAC的速度应该尽可能快, 且噪声低、线性度高、附加性相位噪声非常低。这些性能规格中的任何一项如果缺失, 那么所产生的波形都不足以满足应用的要求。

### 带宽

在任何信号发生应用中, 最重要的设计标准都是带宽。任何设计师都会问到的第一个问题是: 需要多大的带宽来产生想要的信号? 对于特定信令协议或特定应用, 设计师可能需要一定大小的带宽。无论设计师想要实现的带宽有多大, DAC的速度都要至少是想要带宽的2倍。带宽与采样率( $f_s$ )之间的这种关系是由哈里·奈奎斯特定义的, 描述了信号在采样系统中的表现。

尽管可以产生带宽从DC至 $f_s/2$ 的信号, 但是这么做常常不实际, 因为输出频谱中会出现所产生信号的镜频信号。镜频信号会出现在 $N \times f_s \pm f_{out}$ (其中,  $f_{out}$ 是所产生信号的频率)。实际上, 需要重建滤波器来衰减可能出现在输出频谱中任何所产

生信号的镜频信号。即使所产生信号的带宽没有延伸到 $f_s/2$ , 但接近于它, 镜频信号也会难以滤除。重建滤波器是用真实元件在模拟域实现。与数字滤波器不同, 这些元件是非理想的, 会导致具纹波及插入损耗的非理想通带。一般而言, 这些滤波器阶数越高, 产生的纹波和插入损耗就越大, 从而使理想滤波器更加难以设计。信号带宽越接近 $f_s/2$ , 滤波器阶数就必须越高, 以衰减采样过程中产生的镜频信号。滤波器阶数越高, 所需元件就越多, 也就会产生更大的插入损耗和通带纹波。

运用采样速率较高的DAC会增大可用带宽, 这将降低对滤波器的要求, 允许滤波器采用较少的元件, 降低复杂性, 从而简化设计, 产生更好的结果。LTC2000是

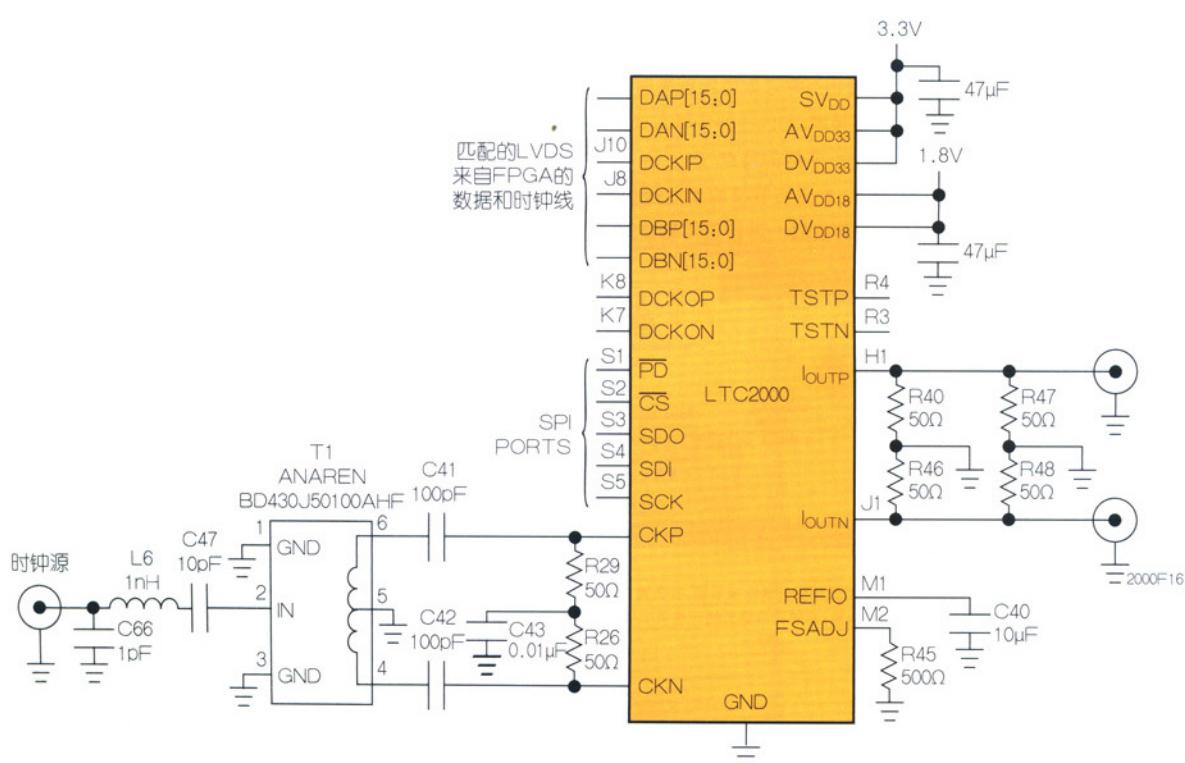

图1: LTC2000建议原理图。

# EDN 电子技术设计

EDN-China

## 技术论坛

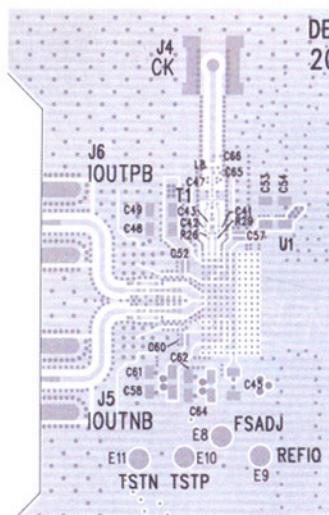

图2: LTC2000建议布局。

一款高性能、16位、2.5Gps高速DAC，具有2.5Gps采样率，从而 $f_s/2$ 频率为1.25GHz。因此，对于800MHz的信号带宽，在1.7GHz处会有一个镜频信号。在想要的频带和镜频信号频率之间有900MHz。凭借900MHz的保护带，镜频信号可以用简单的低通滤波器轻松滤除。具有较低采样速率的DAC所产生的镜频信号更靠近想要的频率，因此需要更加严格和复杂的滤波器。

要产生带宽延伸到 $f_s/2$ 的信号，还有另一个问题，即任何DAC都存在SINC( $\sin(x)/x$ )滚降，随着频率升高，这个问题将使所产生的信号衰减。这种滚降在采样频率( $f_s$ )处有一个零点，从而不可能产生一个准确出现在采样频率上的信号。所产生的信号只是一个DC电压。对于实际应用而言，大约60%的奈奎斯特区域(DC至 $f_s/2$ )没有很大的SINC衰减，而可被利用。如果0dB是DC时的信号电平，那么在60%奈奎斯特频率处，信号电平会下降6dB。人们常常在数字域实现这种滚降的反向补偿，以纠正所产生的信号的自然滚降。这使DAC能够产生随频率变化具恒定幅度的波形。如果使用更高速度的DAC，那么SINC函数的滚降会随DAC输出频率的升高而减轻。

### 相位噪声

在信号发生应用中，另一个需要考虑的重要因素是输出的相位噪声。输出信号中

出现的相位噪声限制信号之间的间隔，且可能限制可以实现的调制阶数。在信号发生过程中，相位噪声越大，所产生信号的SNR就越低，其误码率也就越高。抖动可用来衡量信号在时间域的过零准确度。一个完美的信号会在每个周期中的相同时点过零。实际上，这些过零点在时间上会有一定的分散性。如果这种分散性转换到频率域，就可以看到在基音周围以频谱泄漏形式出现的相位噪声。如果有几个音调相互靠近，那么某个音调的SNR可能因其相邻音调的频谱泄漏而劣化，这会使信号误码率变差，降低所产生信号的准确度。通过降低在所产生信号中引入的相位噪声，可以避免这种信号完整性损失。

为了避免给信号发生系统引入相位噪声的最简单方法，是用一个相位噪声极低的时钟来启动。相位噪声较低的时钟传递给所产生信号的相位噪声较低。还有一点很重要，加在所产生信号上的时钟相位噪声的衰减幅度正比于所产生信号频率与时钟采样速率之比。这种正比关系意味着，与通常用高采样频率时钟产生高频信号相比，如果用同样的时钟产生低频信号，就会在输出信号上产生较小的相位噪声。如果所产生的频谱很宽，那么相对于较低频率端，所产生的信号在频谱高端会有更大的相位噪声。

LTC6946是一款频率合成器，不用外部VCO就可产生从370MHz直至5.7GHz的信号。该器件具备卓越的相位噪声性能和非常低的寄生分量，适合作为信号发生应用的时钟源使用。用LTC6946驱动LTC2000高速DAC时，所产生的相位噪声足够低，适合大多数要求严苛的信号发生应用。LTC6946含有一个内部VCO，可在便利性和相位噪声之间做出权衡。如果使用LTC6945和一个外部VCO，还能实现更低的相位噪声。就LTC6945和LTC6946频率合成器而言，起主导作用的相位噪声源是VCO。在产生65MHz输出音调时，LTC2000在1MHz偏移有 $-165\text{dBc}/\text{rHz}$ 附加噪声。这确保与LTC2000本身的附加性相位噪声相比，时钟相位噪声起主导作用。为了避免其他噪声导致输出信号劣化，在模拟输出电路部分应该注意使用恰当的布局方法。

### 恰当的RF布局

设计印刷电路板时，如果没有采用恰当的设计及布局规则，那么使用高性能DAC和时钟源的好处就会大打折扣。如果没有恰当的对称性、旁路和势垒，所产生的模拟输出波形就有可能出现误差，还可能引入噪声及其他寄生分量。图1显示了LTC2000的典型原理图。就直至500MHz的信号而言，LTC2000的噪声频谱密度好于158dBm/rHz，这有助于在很宽的信号频率范围内保持很高的信噪比。该器件的无寄生动态范围(SFDR)直至500MHz均好于74dB，而对于直至1GHz的输出频率而言，SFDR则好于68dB。为了最大限度提高LTC2000的性能，需要进行恰当的布局。DAC的输出应该作为一个差分对来对待，并尽可能以对称的路径传送。输出网络中的任何非对称性都可能导致差分信号之间出现压差。这种电压差将导致共模干扰，进而使输出频谱中产生不想要的失真和噪声。通过使每个输出的传输线实现对称性，可以避免这种干扰。

可以通过通孔以及良好的布局保护模拟输出免受干扰信号影响。信号发生DAC有3个端口，并带来了布局挑战：时钟输入、模拟输出和数据输入。如果数据输入走线靠近输出或时钟，那么数据信号会耦合到这些信号中，在输出频谱中引起杂散噪声。类似地，如果时钟信号由于不良布局而耦合到模拟输入中，就会影响所产生信号的完整性。设计电路板时，通过在数字电路、时钟信号和模拟输出电路之间设置恰当的势垒，可以使DAC实现最高性能。恰当的做法是在不同的层上传送数字信号、时钟信号和模拟输出，以最大限度降低这些信号之间的相互影响。图2显示了LTC2000的布局，同时显示了怎样隔离数字信号、时钟信号和模拟输出。在该图中，数字走线布设在电路板内层上，仅通过通孔连接到LTC2000焊盘。时钟走线非常短，由通孔包围以隔离信号，而且不会布设在数字走线或模拟输出旁边。输出走线要尽可能对称，并由保护模拟输出免受干扰信号影响的势垒包围。遵循这些布局指导原则并采用干净的采样时钟，LTC6946和LTC2000就能产生非常干净的波形，满足要求最严苛的信号发生应用的需求。EDN

global sources

环球资源属下刊物

# EDN 电子技术设计

EDN-China

## 技术论坛

图2: LTC2000建议布局。

一款高性能、16位、2.5Gps高速DAC，具有2.5Gps采样率，从而 $f_s/2$ 频率为1.25GHz。因此，对于800MHz的信号带宽，在1.7GHz处会有一个镜频信号。在想要的频带和镜频信号频率之间有900MHz。凭借900MHz的保护带，镜频信号可以用简单的低通滤波器轻松滤除。具有较低采样速率的DAC所产生的镜频信号更靠近想要的频率，因此需要更加严格和复杂的滤波器。

要产生带宽延伸到 $f_s/2$ 的信号，还有另一个问题，即任何DAC都存在SINC( $\sin(x)/x$ )滚降，随着频率升高，这个问题将使所产生的信号衰减。这种滚降在采样频率( $f_s$ )处有一个零点，从而不可能产生一个准确出现在采样频率上的信号。所产生的信号只是一个DC电压。对于实际应用而言，大约60%的奈奎斯特区域(DC至 $f_s/2$ )没有很大的SINC衰减，而可被利用。如果0dB是DC时的信号电平，那么在60%奈奎斯特频率处，信号电平会下降6dB。人们常常在数字域实现这种滚降的反向补偿，以纠正所产生的信号的自然滚降。这使DAC能够产生随频率变化具恒定幅度的波形。如果使用更高速度的DAC，那么SINC函数的滚降会随DAC输出频率的升高而减轻。

### 相位噪声

在信号发生应用中，另一个需要考虑的重要因素是输出的相位噪声。输出信号中