## 几乎无噪声、适用于成像应用的 ADC 驱动器

凌力尔特公司 Derek Redmayne

无论就采样率还是就信噪比而言，CCD(电荷耦合器件)和其他传感器对数字转换器都有很高的要求。传感器输出一般是以地为基准的一系列模拟电平(像素)，在像素的边沿之间可能出现瞬态信号。像素数量增加时，捕获图像所需的ADC采样率也随之提高，就大多数大动态范围应用而言，20Msp/s流水线型ADC是足够的。为确保所采样信号具备最高SNR性能，ADC的驱动电路必须提供低阻抗、快速稳定以免引入宽带噪声以及对传感器呈现高输入阻抗。

本文描述一种用于传感器和高性能ADC之间的接口电路，该接口电路不会损害SNR性能。LTC2270 16位流水线型ADC系列适用于高端成像应用。该系列器件具备84.1dB SNR，对成像应用非常有吸引力，这些器件还同时具有非常好的SFDR(超过100dB)。输入范围为2.1Vp-p，远小于大多数成像器件的输出，因此需要衰减和电平移位。

这些ADC的输入必须用良好平衡的差分驱动信号来驱动。通常可从传感器获得的单端驱动会迫使内部虚拟接

地吸收共模输入电流，这可能引起性能下降。这些ADC还是功率非常低的器件，仅为每通道80mW。差分驱动实际上是低功率运行的基础，因为单端驱动需要额外的功率，以在ADC中保持一个稳定的内部基准点。这些器件用1.8V电源工作，这决定了相应的输入范围，如果没有其他因素要求必须这么做，那么就远离这一电源轨吧。远离这一电源轨对防止差分相差很重要，差分相差常常与内部保护二极管的压变电容有关。

这就是困境所在：既能执行单端至差分转换又不损害ADC SNR的差分放大器必然具有低的输入阻抗(或电阻值很小的电阻器)，由于这种差分放大器必须快速稳定至16位准确度，所以其功耗有可能达到4倍于ADC本身功率的量级。LTC6409差分放大器是一个产生良好结果的典范，但仅消耗260mW功率，因此仅为了实现电平移位，就要求周围的网络消耗大约40mW功率。此外，为了实现低噪声和保持相位裕度，需要电阻值相对较低的电阻器，这种电阻器也会消耗信号功率。

结果，这类差分放大器具有很低的

输入阻抗。为了向CCD提供高阻抗而需要的缓冲器也造成了一种困境。该缓冲器必须具有低噪声，能在不到25ns时间内稳定，能以足够大的dV/dt转换以在瞬态时保持闭环工作。此外，该缓冲器必须能驱动低输入阻抗差分放大器。然而，应用要求低功耗。如果期望放大器用单电源轨工作，那么这一困境会更严重。

大多数差分放大器都有若干问题，因为它们或者需要在放大器之后进行一定程度的频带限制，以至于稳定时间受到损害，或者在增益低于1(噪声增益低于2)时不是非常稳定，因此往往会振铃。很多这类放大器与1.8V ADC不是共模兼容的，或者它们没有足够的空间来容纳双端接滤波器或允许在放大器之后进行电平移位。LTC6404是一个很好的案例。该器件在单位增益时是稳定的，不像有些器件那样会振铃，有可能与放大器之后的衰减器一起使用，但是输入参考噪声是1.5nV。相比之下，LTC6409的输入参考噪声为1.1nV。LTC6404的噪声密度峰值频率远高于100MHz，该器件消耗175mW，而且与LTC2270所要求的900mV共模电压

并不真正兼容。如果在该器件之后有一个滤波器并进行电平移位，那么阻抗就会大到一定程度，需要消耗大约80mW功率，从而使分压器中的电压下降。该放大器有可能用+3.3V和-2V电源工作，以解决共模兼容性，而且在放大器之后无须电平移位，就可产生更大的信号摆幅。但是负电源常常不是设计师可以接受的。

放大器可用的稳定时间也许不是整个时钟周期。电源也许决定了这一点，但是存在一个ADC在相反的时钟边沿上产生的干扰，即使放大器未受干扰，这也会使滤波器仅有1/2时钟周期的稳定时间。如果放大器受到这种事件的干扰，那么它就不会给滤波器留下很多的稳定时间。

为了稳定到16位，简单的R C需要大约14个时间常数，就20Msps 而言，这会导致大约90MHz的带宽。随着稳定过程的发生，放大器由于采样，会受到一定程度的干扰，这意味着，简单后置滤波器的带宽必须扩展至130~150MHz，以给放大器留出一定的稳定时间来响应这个干扰。不幸的是，这将使得在放大器的峰值频率区域有噪声通过。更高阶滤波器也许能从之前的奈奎斯特(Nyquist)区更显著地降低噪声影响，但是未必会非常快速地稳定。

## 几乎无噪声的解决方案

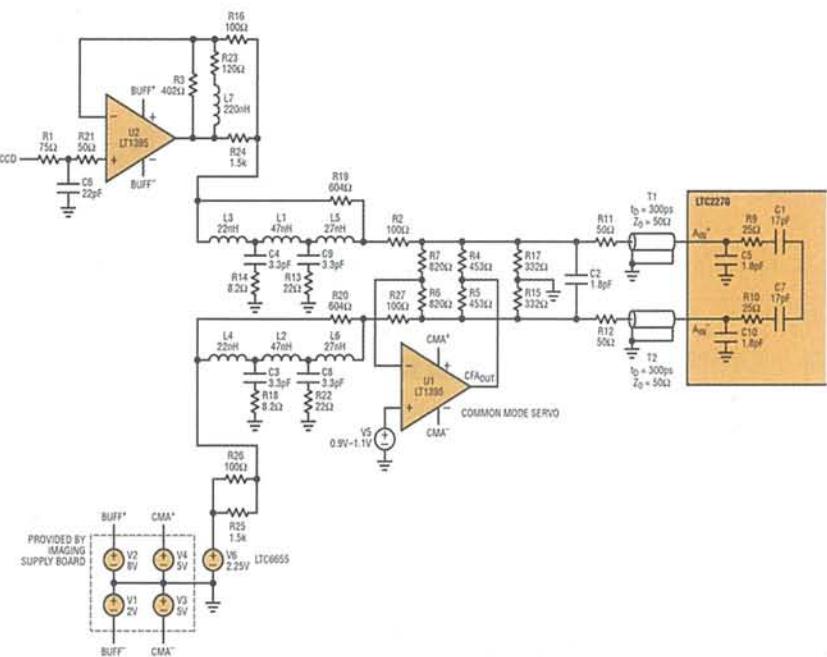

图1中的电路是我们建议的一个驱动电路,该电路采用LTC2270系列,几乎不产生SNR损耗,但是在25Msp/s

时，可能在1个像素时间内稳定到16位。 $84.0\text{ dB}$ 的噪声（所有噪声都包括在内）可能导致这样的结果：该电路未必会在一次计数时间内稳定，但是平均多个帧后，可以稳定到16位。

缓冲放大器(U2)是一款电流反馈放大器，实际上用作射极跟随器。尽管功率是从输出提供的，但是大量的输出电流通过 R16获取，所以看起来电流似乎来自射极。

因为与反馈网络相比，向负输入看进去的阻抗较低，所以输出噪声在负输入端被衰减了，因此，负输入噪声电流没有很大贡献。尽管当用作单位增益缓冲器时，这款放大器的电压噪声规格为  $4.5\text{nV}/\sqrt{\text{Hz}}$ ，但是，在电阻值最小的反馈电阻器中的负输入噪声电流会产生  $10.1\text{nV}/\sqrt{\text{Hz}}$  噪声。不过，在这种类似射极-跟随器的工作模式下，电压噪

声结果为 $1.5 \sim 2 \text{nV}/\sqrt{\text{Hz}}$ 量级。

该放大器附近有一个反馈环路，这个放大器加上了一个 $400\Omega$ 的最小值反馈电阻器。不过在低频时， $400\Omega$ 反馈阻抗与 R23并联，以减小输出端所需的偏移。但是在高频时，所需的反馈电阻为最小 $400\Omega$ 。

通过R24从输出吸取少量输出功率，这只是为了减小输出所需产生的偏移。不过在很多情况下，这也许不是必需的，例如，在视频信号为0~4V或更小的情况下。

为防将来U2是一个差分放大器，已经针对R24做了一些准备，在U2是差分放大器的情况下，从输出吸取功率是切合实际的。还有几种可能的、取决于所需转换率的可替换方案。低噪声、快速稳定的FET放大器有可能在单电源情况下使用。在使用轨至轨放大器时，

图1 几乎无噪声的电路

正轨可能必须是6V，以避免穿过两个输入级之间的过渡区，这个区域会引起失真。如果采用了LT1395，那么在打算接收0~5V信号时， $V_{CC}$ 必须是7.5~8V， $V_{SS}$ 必须是-2V。

如果不需要在像素之间的满标度阶跃期间稳定，那么也可以使用LT6252等更低功率的放大器。不过，不良像素会渗入其后的像素中。时钟馈通的存在和实际可得到的稳定时间有可能限制放大器的选择。

第二个放大器也是LT1395，但是请注意，这个放大器不可能是双通道LTC1396，除非应用会涉及以地电位为中心的信号。第二级必须用5V和-5V工作，以吸收电流，并执行从大约2.5~0.9V共模的电平移位，以及通过根据控制共模提供差分驱动。假定放大器周围的网络是完全对称的，那么这个放大器引起的噪声和失真大部分被ADC的CMRR抑制了，因为这影响仅体现在共模信号上。

我们开发了一款电源电路板，该电路板从单一5V输入提供所有4个所需的电压。该电源电路能给4个通道供电，不过甚至在-125dBFS时，也不会产生与LT3471使用的1.2MHz开关速率有关的干扰。

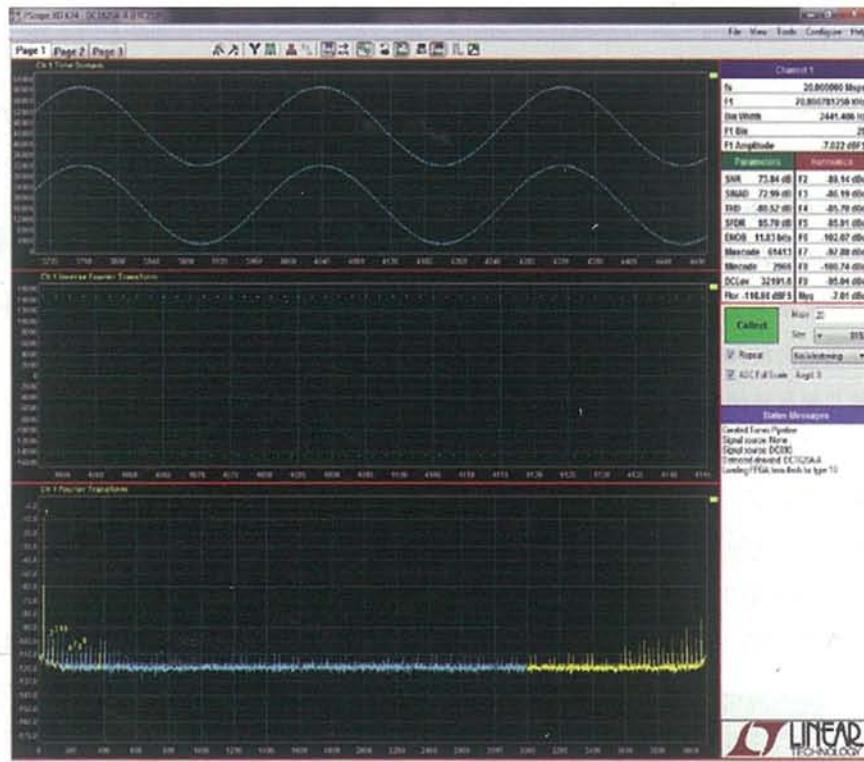

如图2所示，这个驱动器与ADC一起，产生84.0dB SNR，其中包括电源电路板的贡献。以下测试中， $R_1$ 为75Ω，源阻抗为50Ω。这个电路应该适合CCD具有50~200Ω输出阻抗的情况，也应该适合进入保持电容器的电荷

产生数百欧有效阻抗的情况。快速FET缓冲器的使用可允许非常高的源阻抗。

如果CCD出现瞬态时 $dV/dt$ 超过了LTC1395的转换率，或存在RFI，那么就需要22pF的C6。CCD容许这么大幅度的电容负载。如果LTC1395的输出级速度跟不上，那么输入保护二极管的导通就会极大地降低输入阻抗。这种导通几乎在任何反馈放大器中都会发生。而且，如果电荷传送机制暴露于这一输入电流之下，可能即使是在CCD中缓冲一下，这种导通也会造成误差。如果C6和放大器之间的距离延长，那么可能需要R21作为源终接电阻器。

图2 成像电路板原型

图3 0.5平方英寸、4输出电源原型

这种拓扑仅在与输入范围大约为2VP-P的ADC一起使用、且CCD信号在0~4V或0~5V量级时是切实可行的。通过控制共模模式产生平衡-不平

衡转换需要衰减，而该拓扑利用了这种衰减。这种情形类似于传输线平衡-不平衡转换器，在这种转换器中，如果输入和输出端口之间的高共模阻抗对称终止于AC地，那么该共模阻抗会产生平衡驱动。

如图3所示滤波器产生类似高斯噪声的响应，在大约40MHz时下降3dB。该滤波器独立复制两次，以提供一个对称网络，保持U1的误差贡献以共模形式出现。

R7、R4和R17以及与它们相对应的组件满足U1的稳定性要求，将0~5V信号衰减至±1V，并产生电平移位。这些组件实际上可以放置在ADC之后，用作端接组件，这能略微缩短稳定时间。模拟实验表明，如果在CCD和ADC之间有很长的距离，那么在取代R16的一对50Ω电阻器之间的传输路径可以延长。如果距离在30cm至大约60cm之间，那么电缆阻抗应该为75Ω。然后电源终接电阻器也会是75Ω，而另一边为25Ω。如果可能，PCB走线应该高于75Ω。

例如，如果这是打算驱动LTC2185，那么可能有350ps的传输路径。如果使用LTC2270系列，那么17pF采样电容器要求这条传输线(图1中的T1和T2)应该少于40ps(大约1cm)。

除了在20MSPS和25MSPS时数字化1/4FS~1/2FS的小偏移频率，为了证实这个电路可以用于CCD信号，还进行了多项测试，包括：300kHz、-1dBFS正弦波(2阶和3阶-90dB

图4 双音测试：70kHz、7.022dBFS正弦波

图5 在70kHz上所加功率相同，但是去除奈奎斯特频率上的功率

SFDR)，代表CCD信号中的dV/dt；接近满标度且具附加在200kHz、-20dB正弦波的方波(10MHz和5MHz)。结果显示，在成对的“黑白像素”中，在由大的同步偏移产生的正弦波上没有失真。

请注意图4时间域曲线中两个波形的形状，这两个波形是由方波中两个电平之间每隔一个采样转换一次引起的。

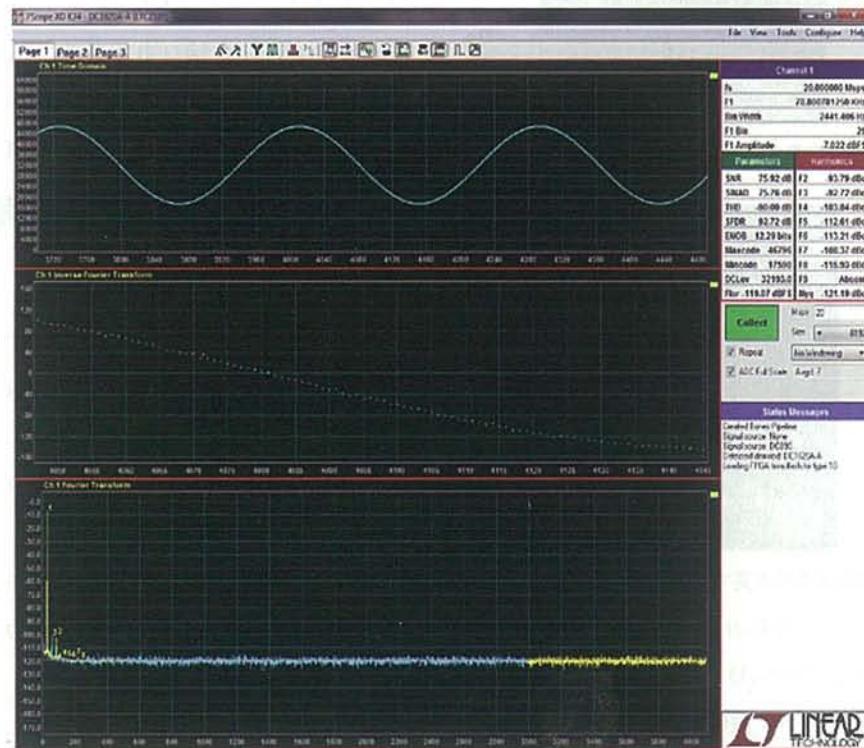

在时间轴上放大倒转的FFT窗口，通过有选择地屏蔽70kHz区域的功率，可以仅显示在奈奎斯特频率上的音调。

图5显示，在低频音调中没有明显的功率变化，仍然为-7.022dBFS，仅在失真分量中有相对较小的变化。这证明，增加一个幅度较大的方波不会引起峰值压缩。人们相信，附加在1/2FS方波上的70kHz音调代表了dV/dt和稳定情况，而这也代表了靠近像素终端采样所得CCD波形中看到的结果。

## 结论

如果在成像应用中需要一个具备高SNR的ADC，那么就需要单端至差分转换，以获得从CCD到ADC的信号。该转换必须衰减信号摆幅，并在不附加很大噪声的情况下，提供一个非常稳定的共模输出电平。本文提出的电路刚好可以满足这种要求。该电路采用一个低功率ADC，ADC的数据表SNR性能规格为84.1dB，所实现的SNR为84.0dB，这意味着，该转换几乎是无噪声的。