特刊：模拟及数字IC

## 寻找合适的基准时钟分配

凌力尔特公司 Michel Azarian

在RF接收器中，通过基准时钟缓冲和分配引入的时钟抖动可能限制可实现的系统性能。为了获得宽松的前端滤波器要求而采用相对较高的中频(IF)时，对低抖动的要求会进一步提高。本文详细探讨了325MHz IF采样系统的设计，并提出了将正弦波基准信号转换为一对差分LVPECL时钟的时钟缓冲器和分配器，该时钟缓冲器和分配器适用于驱动高速ADC，而且驱动高速ADC时，最大限度地减小了所引入的抖动。

### 系统描述

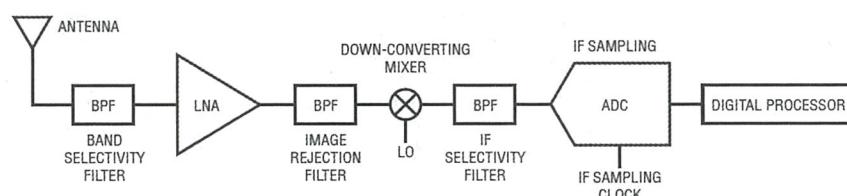

在IF采样(或欠采样)系统中，ADC完成RF接收器中最后一级下变频。IF越高，RF前端的镜频抑制滤波器的陡度就越小，这有助于减小滤波器的成本、尺寸和插入损耗，并进一步减少对放大的需求，这反过来会导致更低的成本和功耗。图1所示为一个典型和采用IF采样的RF接收器链路。

设计接收器时，采用相对较高 IF

的缺点是，在对较高频率的模拟输入信号采样时，系统性能规格更容易受到ADC性能降低的影响。例如，在输入频率较高时，ADC的无寄生动态范围(SFDR)变差了。更重要的是，在对更快速的输入采样时，ADC的孔径抖动和时钟抖动相结合，限定了可实现的信噪比(SNR)。

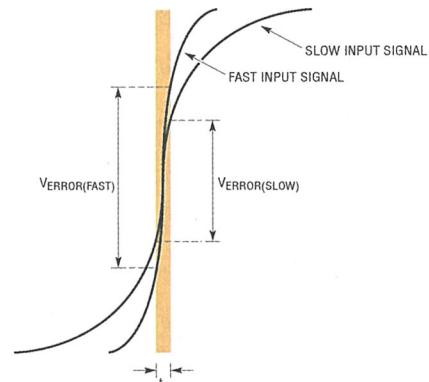

时钟抖动的影响可以通过比较由于时钟抖动所引起的电压误差值、同时采用相同的ADC和时钟对两个摆动信号(其中一个信号的斜率高于另一个信号)进行采样来演示。该时钟具有相同的时间抖动量( $t_d$ 的单位为s-RMS)，并按图2所示对两个信号实施采样。对于移动速度较快的信号，因时钟抖动而引起的不确定性确实较高，因此，当模拟输入具有较高的频率分量时，时钟抖动是一个限制SNR指标的主要(如果不是主导的话)误差源。所以，尽可能地抑制ADC时钟(在图1中表示为IF采样时钟)的抖动是最重要的。

图1 典型单IF级RF接收器方块图

图2 在对缓慢和快速摆动信号进行数字化处理的过程中时钟抖动所造成的影响

为了避免在ADC时钟输入端上发生AM至PM噪声转换，该时钟应具有一个高的摆率，理想情况下是一个方波。ADC的时钟输入起一个限幅器的作用，其获取一个信号并通过在输入信号的零(或某些其他的基准)交叉点上做出决策来对此信号进行方波处理。当输入信号具有一个缓慢的摆率时(比如在一个低频和/或低幅正弦波中，与方波相比，信号通过零交叉点类似于慢动作)，将发生AM至PM噪声转换。假如存在任何类型的AM噪声(例如，电阻器热噪声，来自于电源的耦合噪声等)，则输入信号的零交叉点在随后的脉冲边缘之间变得不一致，从而导致在限幅器的输出端上产生抖动；于是，AM噪声转换为PM噪声。反之，倘若输入信号

快速通过零交叉点（比如，LVPECL信号由于其具有快速上升和下降时间的原因一般都将如此），那么加至时钟的AM噪声被转换为PM噪声的机会就非常之少，甚至完全没有机会。

另外，大多数新式ADC要求以差分方式驱动时钟输入，以实现最佳性能。时钟信号走线在PCB上常常经过相当长的距离，因为信号的源和目的地相互之间通常不是靠得很近。与单端时钟信号传送相比，以差分形式传送时钟信号可使信号不受耦合影响，而且能全面提升设计的可靠性。

图1所示LO信号一般由锁相环（PLL）系统产生。PLL需要一个基准时钟，以将LO锁定在该时钟上。传统上，10MHz是常见的基准频率。不过，频率高得多的基准时钟如今变得越来越普遍了。事实上，100MHz以及更高的频率在新式RF设计中并非不常见。

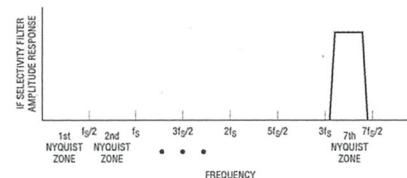

基准时钟通常由OCXO或TCXO器件产生，这种时钟的抖动（或相位噪声）一般非常小。如果PLL基准时钟的频率合理选择为高于RF接收通道带宽（或在两个或更多相邻通道同时数字化的接收器中，为多个通道的带宽）的两倍，那么同样的基准信号还可用作IF采样ADC的时钟，以符合某些适合的频率规划。理想情况下，IF选择滤波器的通带及其过渡区域的大部分都应在ADC的单一奈奎斯特（Nyquist）区域内，以避免频率折叠。用图3所示的IF滤波器幅度响应，可以说明这一点。在

图3中，所选IF与ADC的7阶奈奎斯特区域相匹配。在该图中， $f_S$ 代表ADC的采样率。在这种情况下，会选择图1中的LO，这样，混频器的下变频信号输出就会以IF选择滤波器的中间点为中心，如图3所示。

图3 IF滤波器幅度响应（对于一种可避免频率折迭的ADC采样速率）实例

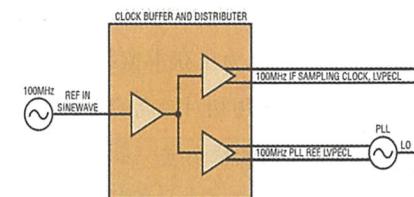

图4总结了上述时钟分配方案，图中假定基准频率为100MHz。图4中的时钟缓冲器和分配器在这个系统中起着重要的作用，因为它接收来自OCXO或TCXO器件的单端正弦波，并提供两个差分LVPECL信号，这两个信号适合发送到ADC和PLL。为了使在所分配的时钟上附加的抖动最小，它应该这么

做。LTC6957-1是一款附加抖动很小的双LVPECL输出时钟缓冲器，适用于这种要求附加抖动较小的应用，并满足上述讨论中提出的所有要求。运用不同版本的LTC6957，还可以实现其他输出格式。LTC6957-2提供LVDS输出，LTC6957-3和LTC6957-4提供CMOS输出。

图4 基准时钟分配方案

## 电路实现

正如之前所讨论的那样，抖动是提高IF的主要限制因素之一。用常见ADC和LTC6957-1构成时钟分配器时，能实现什么样的性能？为了确定这

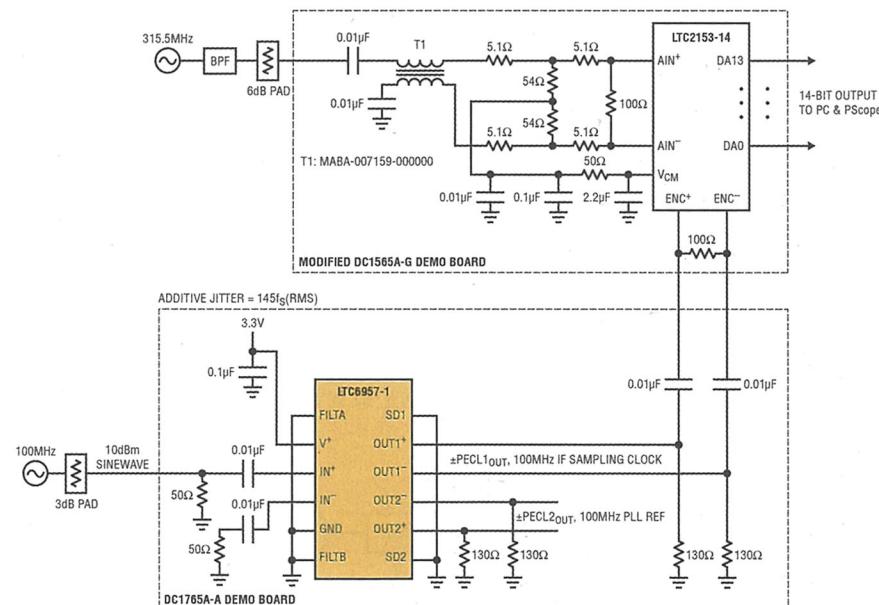

图5 IF采样系统原理图

一点，我们修改了两款凌力尔特演示电路板，并将两块演示电路板连接起来，如图5所示。

LTC2153-14是一款310Msps、14位ADC，该ADC为高的模拟输入频率工作而进行了全面规定，从而使其适合在这应用中作为IF采样ADC使用。其演示电路板DC1565A-G修改后如图5所示。

演示电路DC1765A-A采用了LTC6957-1，用来缓冲100MHz OCXO的正弦波输出。DC1765A-A的两对差分LVPECL输出之一连接至DC1565A-G的差分编码时钟输入。第二对差分信号可以用作图1中LO产生PLL信号的基准输入。

考虑到该ADC的时钟频率为100MHz，所以在避免混叠的同时，理论上能实现的最大带宽为50MHz。如图3所示，选定了7阶奈奎斯特区域，这

意味着，这个50MHz理想带宽涵盖了300~350MHz频率范围。这就需要理想的砖墙式带通滤波器，且滤波器的中心频率为325MHz，通带为50MHz，以仅允许300~350MHz范围内的IF信号通过，同时抑制其他所有在想要的频带中可能引起混叠和干扰的信号。

在一个实际滤波器中，除了中心频率容限，由于滤波器通带和阻带区域之间的过渡区域并非无限小，所以在这种情况下，更合理的IF带宽选择也许是例如带宽高达30MHz、中心频率为325MHz的表面声波(SAW)滤波器。目前，越来越容易买到这一频率范围的SAW滤波器了。

### 性能总结

通过一个类似于IF选择性滤波器的BPF和一个衰减器(其用于把ADC所承受的幅度调整至-1dBFS)将一

个315.5MHz测试音调连接至改良型DC1565A-G的模拟输入。

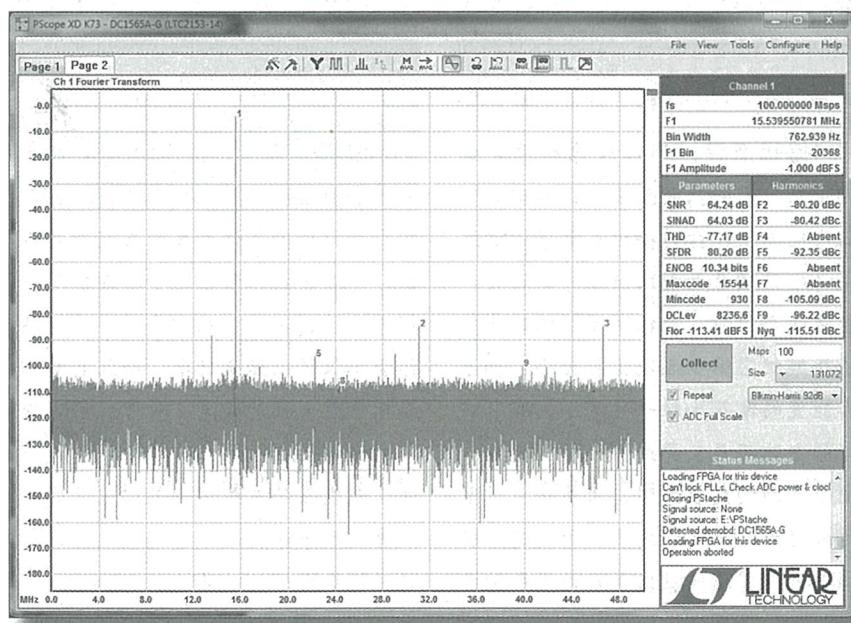

DC1565A-G通过USB连接至一台PC，这里，PScope数据采集控制软件用于监视两个影响接收器质量的关键性参数：SNR和SFDR。图6示出了运行中的PScopeTM，给出了当采用315.5MHz、-1dBFS音调作为ADC的模拟输入，并利用作为ADC编码时钟的LTC6957-1对100MHz LVPECL信号进行缓冲时的131072点FFT以及一些相关的分析。由图6可见，实现的SNR高于64dB，而SFDR则超过了80dB。对于325MHz IF采样器来说，这些指标参数是极其优异的。

由于LTC6957-1的输入是一个100MHz正弦波(为50Ω负载输送+10dBm功率)，因此按照LTC6957产品手册给出的建议，应把有助于输入为低幅度和/或低频率时减小附加抖动量的内部带宽限制滤波器(FILT A和FILT B)均关断。

### 结论

设计并评估了一个作为RF接收器一部分的325MHz IF采样系统。采用低抖动时钟缓冲器和分配器LTC6857-1以LVPECL格式来分配将被用作ADC采样时钟和PLL基准的100MHz系统基准时钟。该IF采样系统的性能通过观察SNR和SFDR数值来测量。利用该系统获得了卓越的64dB SNR和出色的80dB SFDR，从而实现了有助于放宽RF镜频抑制滤波器要求的较高IF采样。

图6 PScope的屏显图